ПЛИС FPGA серии Cyclone V GT компании Altera стали первыми в отрасли устройствами, которые соответствуют спецификации PCIe Gen2 для передачи данных на скоростях до 5 Гбит/с |

|

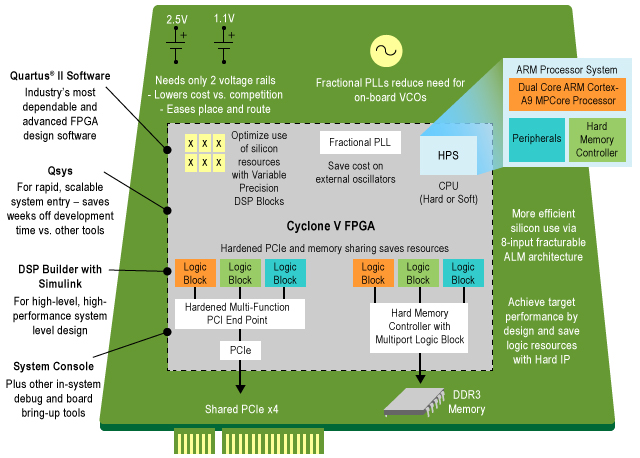

Компания Altera Corporation объявила об успешном завершении тестирования ПЛИС FPGA серии Cyclone V GT на соответствие требованиям спецификации протокола PCI Express® (PCIe®) 2.0. Серийно производимые на сегодняшний день, устройства серии Cyclone V GT это первые в отрасли недорогие, малопотребляющие ПЛИС FPGA, поддерживающие передачу данных по интерфейсу PCIe 2.0 на скоростях до 5 Гбит/с.

|

ПЛИС серии Cyclone V GT успешно прошли все тесты на соответствие требованиям консорциума PCI-SIG® и добавлены в список интеграторов PCI-SIG Integrators List. Устройства серии Cyclone V GT позволяют значительно снизить стоимость системы и уровень ее энергопотребления при разработки приложений с интерфейсом PCIe Gen2, по сравнению с ПЛИС FPGA предыдущих поколений.

ПЛИС серии Cyclone V GT интегрируют аппаратные приемопередатчики, поддерживающие скорость передачи данных до 5 Гбит/с, и имеют два специализированных IP-блока функций, уже реализованных в схеме ПЛИС. Реализованные IP-блоки протокола PCIe позволяют повысить функциональность и производительность системы при одновременном снижении сложности ее разработки. Аппаратные IP-блоки протокола PCIe 2.0 включают контроллер доступа (MAC) и физический уровень (PHY), а также слои обмена данными и транзакций. Блоки допускают функционирование, как в качестве оконечного устройства, так и в качестве порта расширения, поддерживая при этом до 4 линий обмена данными.

ПЛИС типа «Система-на-Кристалле» (SoC) серии Cyclone V имеют инновационную функцию, позволяющую объединить до восьми точек доступа PCIe в одно оконечное устройство, которое будет поддерживаться набором стандартных драйверов. Данная особенность крайне полезна при разработке таких приложений, как порты расширения линий ввода/вывода, значительно экономя время на написание специализированных драйверов. ПЛИС FPGA серий Cyclone V и Cyclone V SoC также поддерживают инновационную функцию компании Altera “Конфигурация по Протоколу» (Configuration via Protocol) посредством PCIe интерфейса, что позволяет аппаратному IP-блоку PCIe функционировать вне зависимости от того, что реализовано в логической схеме ПЛИС. Это гарантирует, что оконечное PCIe устройство будет проиндексировано в течение необходимых 100 мс, как того требует спецификация протокола PCIe, независимо от используемого метода конфигурации.

|

Компания Altera предлагает полный спектр PCI-SGI совместимых решений для всех своих устройств, оптимизированных под ключевые требования приложений. Решения компании включают конфигурируемые IP-блоки функций, демонстрационные комплекты и инструменты разработки для создания оконечных устройств, мостов, коммутаторов и корневых портов. Новейший отладочный комплект для ПЛИС FPGA Cyclone V GT от компании Altera обеспечивает быструю реализацию протокола связи PCIe Gen2, снижая риски и время проектирования. Отладочный комплект предлагает быстрый и эффективный способ разработки недорогого энергоэффективного решения системного уровня на базе ПЛИС FPGA и скорейшего достижения конечного результата.

Доступность

ПЛИС FPGA серии Cyclone V GT выпускаются серийно. Компания Altera предлагает самую широкую линейку недорогих малопотребляющих ПЛИС с технологическими нормами 28 нм, отличающихся объемом от 25 тыс. до 300 тыс. логических элементов (LE) и компактными корпусами, в соответствии с современными требованиями пользователей.

| Источник: gaw.ru | Дата публикации: 30/04/2013 |

|  |

|

Реклама на сайте |

|

Последние новости  |

[06/02/2019] Конференция в МГТУ им. Баумана «Технологии разработки и отладки сложных технических систем» 2019

[09/05/2018] Грандиозная майская распродажа на Gearbest!

[16/05/2017] С 15 по 17 мая в магазине Gearbest проходит грандиозный флэшсейл

[10/05/2017] Так что же такое Спиннер?

[05/12/2016] Новый Год и Рождество с GearBest!

[29/09/2016] Всемирный День Интернета на GearBest

Читать все новости >> |