# Cadence Op-Amp Schematic Design Tutorial for TSMC CMOSP35 $\,$

Till Kuendiger, Joseph Schrey, Iman Taha, Yi Lin, Tao Dai, Li Liang, Song-Tao Huang, Yue Huang

December 7, 2001

# Contents

| Pr       | refac            | e                                                                                                |                                                                                                                                                                                   | $\mathbf{iv}$                                                  |

|----------|------------------|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| 1        | Intr             | oducti                                                                                           | on                                                                                                                                                                                | 1                                                              |

|          | 1.1              | Review                                                                                           | v of CMOS FET's                                                                                                                                                                   | 1                                                              |

|          | 1.2              |                                                                                                  | ng a New Library in Cadence                                                                                                                                                       | 2                                                              |

|          | 1.3              | Schem                                                                                            | atic Capture                                                                                                                                                                      | 4                                                              |

|          |                  | 1.3.1                                                                                            | Virtuoso Schematic Editor                                                                                                                                                         | 4                                                              |

|          |                  | 1.3.2                                                                                            | Virtuoso Symbol Editor                                                                                                                                                            | 5                                                              |

|          |                  | 1.3.3                                                                                            | Affirma Analog Circuit Design Environment                                                                                                                                         | 6                                                              |

|          |                  | 1.3.4                                                                                            | The Waveform Window                                                                                                                                                               | $\overline{7}$                                                 |

|          |                  | 1.3.5                                                                                            | The Cadence Calculator                                                                                                                                                            | 8                                                              |

|          | 1.4              | Genera                                                                                           | ating the Characteristic MOSFET Curves                                                                                                                                            | 9                                                              |

|          |                  | 1.4.1                                                                                            | N-channel Enhancement-Type MOSFET                                                                                                                                                 | 9                                                              |

|          |                  | 1.4.2                                                                                            | P-channel Enhancement-Type MOSFET                                                                                                                                                 | 14                                                             |

|          |                  |                                                                                                  |                                                                                                                                                                                   |                                                                |

| <b>2</b> | An               | Introd                                                                                           | uction to Op-Amps                                                                                                                                                                 | 17                                                             |

| <b>2</b> | <b>An</b><br>2.1 |                                                                                                  | uction to Op-Amps<br>eters of an Op-Amp                                                                                                                                           | <b>17</b><br>17                                                |

| 2        |                  |                                                                                                  | eters of an Op-Amp                                                                                                                                                                |                                                                |

| 2        |                  | Param                                                                                            |                                                                                                                                                                                   | 17                                                             |

| 2        |                  | Param<br>2.1.1                                                                                   | eters of an Op-AmpOffset VoltageInput Current                                                                                                                                     | 17<br>17                                                       |

| 2        |                  | Param<br>2.1.1<br>2.1.2                                                                          | eters of an Op-Amp                                                                                                                                                                | 17<br>17<br>18                                                 |

| 2        |                  | Param<br>2.1.1<br>2.1.2<br>2.1.3                                                                 | eters of an Op-Amp                                                                                                                                                                | 17<br>17<br>18<br>19                                           |

| 2        |                  | Param<br>2.1.1<br>2.1.2<br>2.1.3<br>2.1.4                                                        | eters of an Op-Amp                                                                                                                                                                | 17<br>17<br>18<br>19<br>19                                     |

| 2        |                  | Param<br>2.1.1<br>2.1.2<br>2.1.3<br>2.1.4<br>2.1.5                                               | eters of an Op-Amp                                                                                                                                                                | 17<br>17<br>18<br>19<br>19<br>20                               |

| 2        |                  | Param<br>2.1.1<br>2.1.2<br>2.1.3<br>2.1.4<br>2.1.5<br>2.1.6                                      | eters of an Op-AmpOffset VoltageInput CurrentInput Common Mode Voltage RangeMaximum Output Voltage SwingOutput ImpedanceCommon-Mode Rejection RatioSupply Voltage Rejection Ratio | 17<br>17<br>18<br>19<br>19<br>20<br>20                         |

| 2        |                  | Param<br>2.1.1<br>2.1.2<br>2.1.3<br>2.1.4<br>2.1.5<br>2.1.6<br>2.1.7                             | eters of an Op-Amp                                                                                                                                                                | 17<br>17<br>18<br>19<br>19<br>20<br>20<br>21                   |

| 2        |                  | Param<br>2.1.1<br>2.1.2<br>2.1.3<br>2.1.4<br>2.1.5<br>2.1.6<br>2.1.7<br>2.1.8                    | eters of an Op-Amp                                                                                                                                                                | 17<br>17<br>18<br>19<br>19<br>20<br>20<br>20<br>21<br>21       |

| 2        |                  | Param<br>2.1.1<br>2.1.2<br>2.1.3<br>2.1.4<br>2.1.5<br>2.1.6<br>2.1.7<br>2.1.8<br>2.1.9<br>2.1.10 | eters of an Op-Amp                                                                                                                                                                | 17<br>17<br>18<br>19<br>19<br>20<br>20<br>21<br>21<br>21<br>22 |

|      | 2.3.1 Specification                                          |  |  |  |  |  |  |  |  |  |

|------|--------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

|      | 2.3.2 Procedure of Optimization                              |  |  |  |  |  |  |  |  |  |

|      | 2.3.3 Optimize the Parameters of the Op-Amp                  |  |  |  |  |  |  |  |  |  |

|      | 2.3.4 How to get the Quiescent point in a complex circuit .  |  |  |  |  |  |  |  |  |  |

| 2.4  |                                                              |  |  |  |  |  |  |  |  |  |

| a C  |                                                              |  |  |  |  |  |  |  |  |  |

|      | Irrent Mirrors and Biasing Networks                          |  |  |  |  |  |  |  |  |  |

| 3.1  |                                                              |  |  |  |  |  |  |  |  |  |

| 3.2  |                                                              |  |  |  |  |  |  |  |  |  |

| 3.3  |                                                              |  |  |  |  |  |  |  |  |  |

| 3.4  |                                                              |  |  |  |  |  |  |  |  |  |

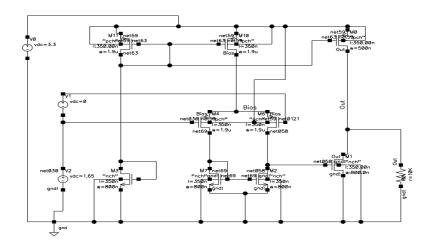

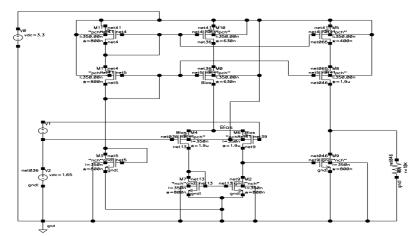

|      | 3.4.1 Basic Current Mirror                                   |  |  |  |  |  |  |  |  |  |

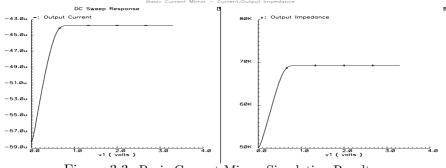

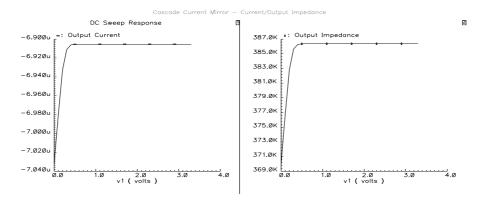

|      | 3.4.2 Cascade/Cascode Current Mirror                         |  |  |  |  |  |  |  |  |  |

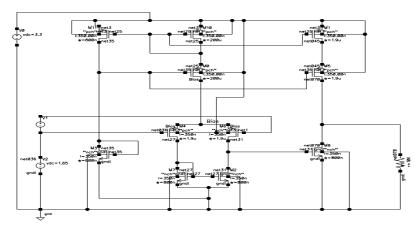

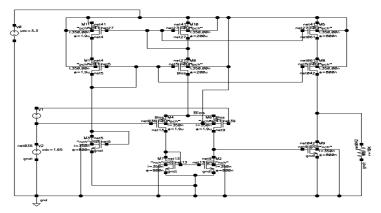

|      | 3.4.3 Wilson Current Mirror                                  |  |  |  |  |  |  |  |  |  |

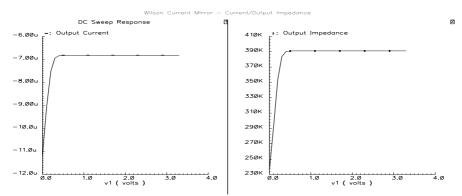

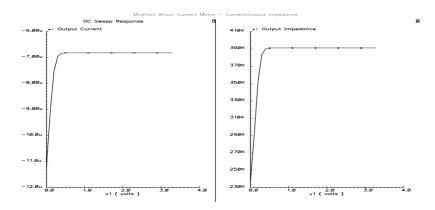

|      | 3.4.4 Modified Wilson Current Mirror                         |  |  |  |  |  |  |  |  |  |

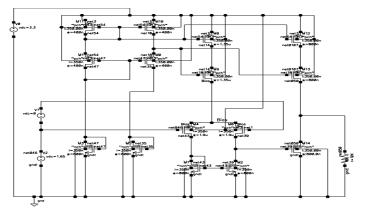

|      | 3.4.5 Reduced Cascade Current Mirror                         |  |  |  |  |  |  |  |  |  |

| 3.5  | Conclusion                                                   |  |  |  |  |  |  |  |  |  |

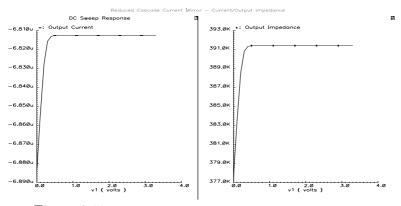

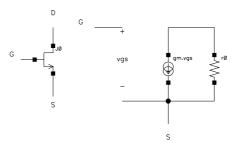

| 4 Di | fferential Input Stage                                       |  |  |  |  |  |  |  |  |  |

| 4.1  |                                                              |  |  |  |  |  |  |  |  |  |

| 4.2  |                                                              |  |  |  |  |  |  |  |  |  |

| 4.3  |                                                              |  |  |  |  |  |  |  |  |  |

| 4.4  |                                                              |  |  |  |  |  |  |  |  |  |

| 4.5  |                                                              |  |  |  |  |  |  |  |  |  |

| 4.6  | 1                                                            |  |  |  |  |  |  |  |  |  |

| 4.7  |                                                              |  |  |  |  |  |  |  |  |  |

| 4.8  |                                                              |  |  |  |  |  |  |  |  |  |

| 4.9  | 0 0                                                          |  |  |  |  |  |  |  |  |  |

|      | 0 The Common-Mode Range                                      |  |  |  |  |  |  |  |  |  |

|      | 1 Important Relationships for The Design                     |  |  |  |  |  |  |  |  |  |

|      | 2 Tradeoffs for Increasing the Gain of the Two Stage Op-Amp. |  |  |  |  |  |  |  |  |  |

|      | 3 Design Methodology for the Two Stage Op-Amp                |  |  |  |  |  |  |  |  |  |

|      | 4 Design Example                                             |  |  |  |  |  |  |  |  |  |

|      | 5 Limitations of the Two Stage Op-Amp                        |  |  |  |  |  |  |  |  |  |

|      | 6 The Cascode Op-Amp                                         |  |  |  |  |  |  |  |  |  |

| 4.1  |                                                              |  |  |  |  |  |  |  |  |  |

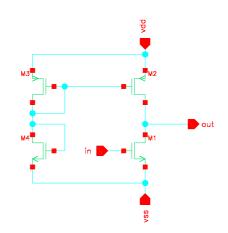

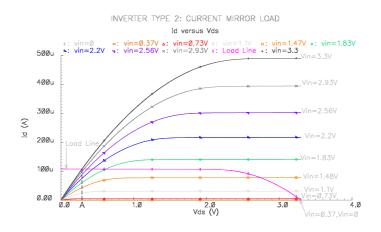

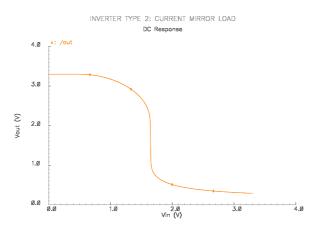

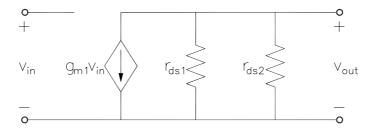

|      | verting Amplifiers                                           |  |  |  |  |  |  |  |  |  |

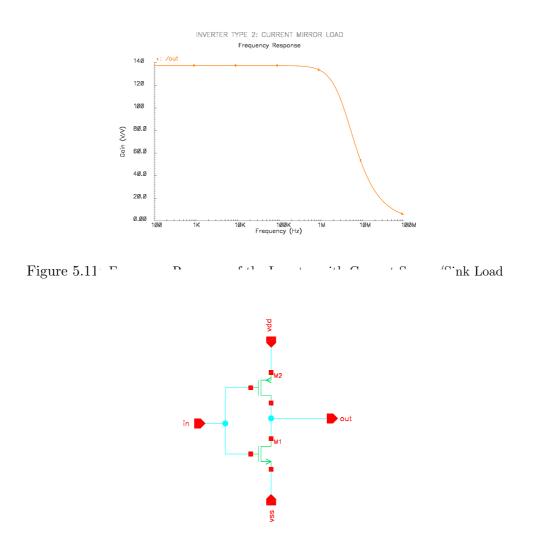

| 5.1  |                                                              |  |  |  |  |  |  |  |  |  |

| 5.2  |                                                              |  |  |  |  |  |  |  |  |  |

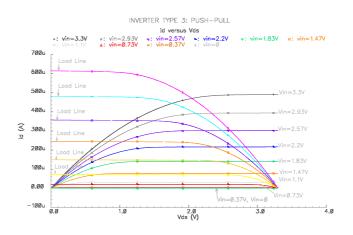

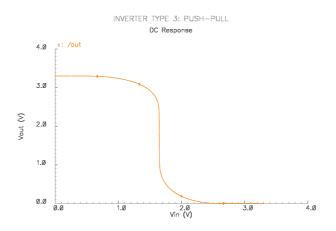

| 5.3  | Push-Pull Inverter                                           |  |  |  |  |  |  |  |  |  |

ii

|   | 5.4  | Comparison                                                    | 92  |

|---|------|---------------------------------------------------------------|-----|

|   | 5.5  | Application                                                   | 92  |

| 6 | Cor  | ntrol Network and Output Stage                                | 95  |

|   | 6.1  | Classification of Output Stage                                | 96  |

|   | 6.2  | Class-A Output Stage                                          | 96  |

|   |      | 6.2.1 Simple output amplifier using a Class-A, current-source |     |

|   |      | inverter                                                      | 96  |

|   |      | 6.2.2 Common-Drain (Source-Follower) Output Amplifier .       | 98  |

|   |      | 6.2.3 Power Analysis                                          | 98  |

|   | 6.3  | Class-B Output Stage                                          | 99  |

|   |      | 6.3.1 Push-Pull, Inverting CMOS amplifier                     | 99  |

|   |      | 6.3.2 Power Analysis                                          | 101 |

|   | 6.4  | Class-AB Output Stage                                         | 101 |

|   | 6.5  | Short Circuit Protection                                      | 102 |

|   | 6.6  | Conclusion                                                    | 103 |

|   | 6.7  | Design Considerations                                         | 106 |

|   |      | 6.7.1 Negative Feedback                                       | 106 |

|   |      | 6.7.2 Frequency Compensation                                  | 106 |

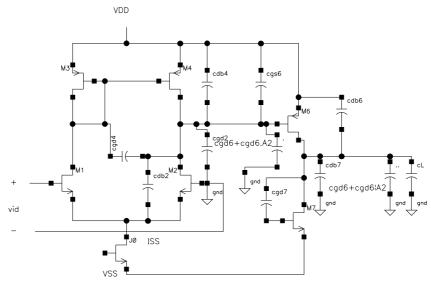

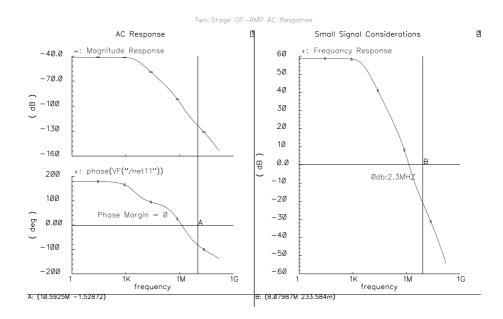

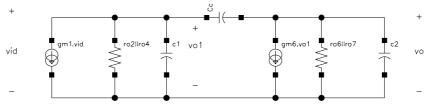

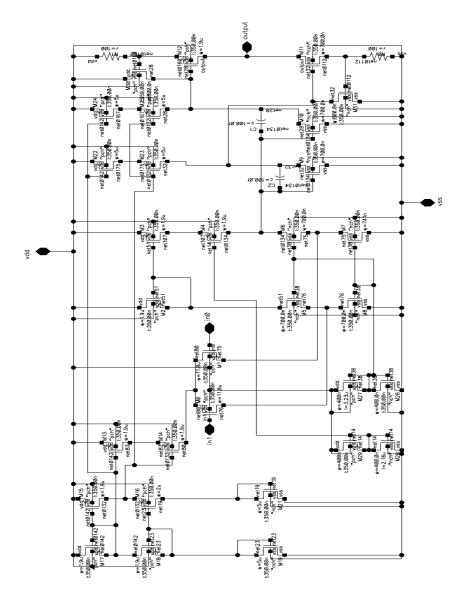

| 7 | Inte | egrating the Sub-Circuits                                     | 108 |

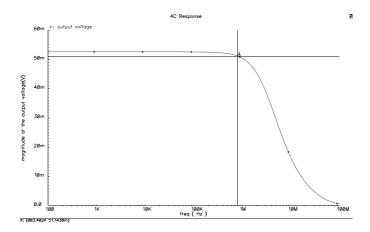

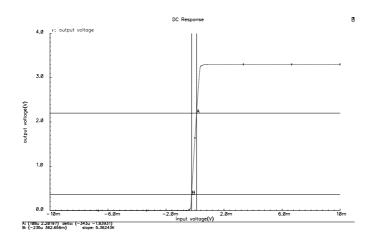

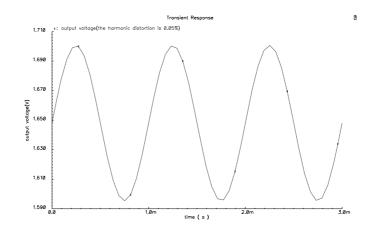

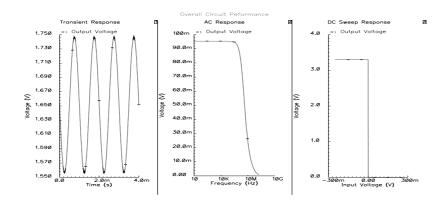

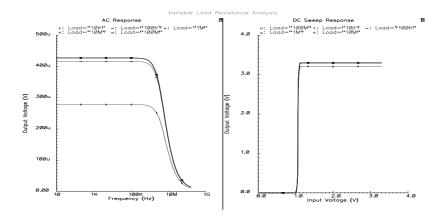

|   | 7.1  | Overall Performance                                           | 109 |

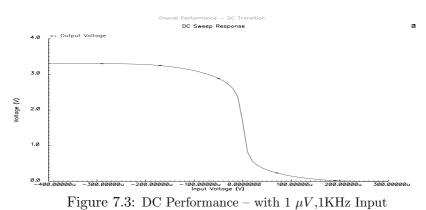

|   | 7.2  | The Measurement of Some Main Parameters                       | 110 |

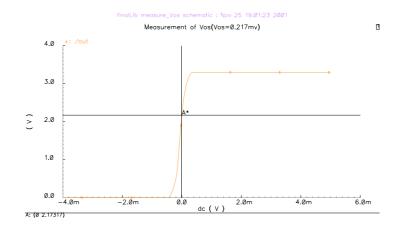

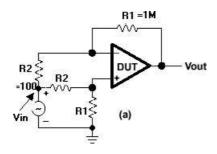

|   |      | 7.2.1 Input Offset Voltage                                    | 110 |

|   |      | 7.2.2 Common-Mode Rejection Ratio (CMRR)                      |     |

|   |      | 7.2.3 Output Resistance - $R_o$                               | 114 |

|   | 7.3  | Delivering Power to the Load/Instantaneous Power              | 117 |

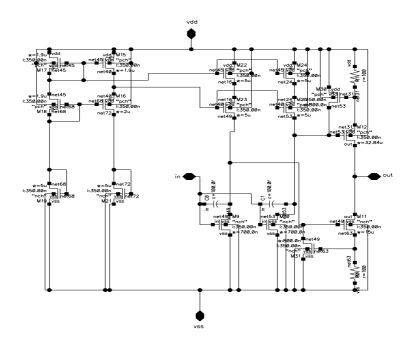

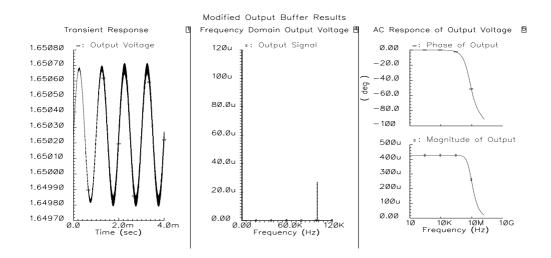

|   | 7.4  | Improving the Output Buffer                                   | 118 |

|   |      | 7.4.1 Stabilizing the Output                                  | 120 |

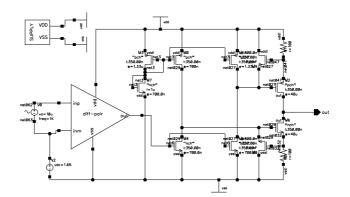

|   |      | 7.4.2 The Final Schematic                                     | 121 |

| 8 | Clo  | sing Remarks                                                  | 122 |

|   | 8.1  | Conclusion                                                    | 122 |

|   | 8.2  | Future Work                                                   | 123 |

| 9 | Bib  | liography                                                     | 124 |

iii

## Preface

The purpose of this document is to familiarize the reader with the Cadence set of tools in order to do analog micro-electronic circuits. The design process will use TSMC's CMOSP35 technology and as a result requires access to the restricted technology files.

### Chapter 1

### Introduction

This tutorial assumes that the user is working in the CMC supplied environment for CMOSP35 design.

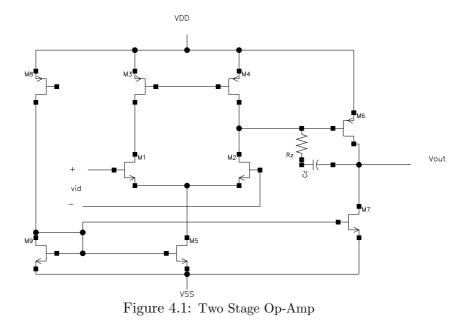

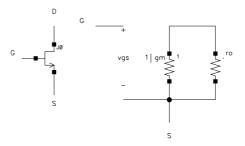

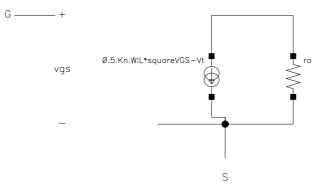

### 1.1 Review of CMOS FET's

The Complimentary Metal Oxide Semi-Conductor Field Effect Transistor is a four terminal device: Base, Emitter, Collector and Substrate. Unlike the Bipolar Transistor the MOSFET is a symmetrical device: the source and drain can be interchanged.

The models which SPICE uses for the CMOSP35 technology are very accurate, however, are too complex to be used by humans. A quick overview of the device operation follows, for a more complete discussion please refer to an appropriate text book. The gate of the device is insulated from the rest of the device, meaning that no current will flow into the gate of a MOSFET. The substrate connection, for an N-channel transistor, is always connected to  $V_{SS}$  (which usually means ground). When the voltage on the gate of the device is large enough an inversion layer forms under the gate, between the drain and source. This means that a channel of charge carriers exists between the two N-type regions. For an N-channel transistor these charge carriers will be electrons. This allows current to flow from the source terminal to the drain terminal. Some generalized relationships are stated below.

$$I_{ds} = \mu_{eff} C_{ox} \frac{W}{L} \left[ \left( V_g - V_{fb} - 2\psi_B - \frac{V_{ds}}{2} \right) V_{ds} \right] - \mu_{eff} C_{ox} \frac{W}{L} \left[ \frac{2\sqrt{2\varepsilon_{si}qN_a}}{3C_{ox}} \left[ (2\psi_B + V_{ds})^{\frac{3}{2}} - (2\psi_B)^{\frac{3}{2}} \right] \right]$$

(1.1)

### **1.2** Creating a New Library in Cadence

Once Cadence has been started the icfb window is shown. This is the main window for Cadence; all messages, including error and warning messages, will be displayed in this window.

| v               | r icfb - Log: /home/vlsi/kuendig/CDSlogs/CDS.log.28050 |         |                 |             |         |      |   |  |  |  |

|-----------------|--------------------------------------------------------|---------|-----------------|-------------|---------|------|---|--|--|--|

| File            | Tools                                                  | Options | Technology File | CMC Gateway | CMOSP35 | Help | 1 |  |  |  |

| ><br>ddsNe<br>t | ewsClos                                                | se ()   |                 |             |         |      |   |  |  |  |

| <u> </u>        |                                                        |         |                 |             |         |      | ~ |  |  |  |

| mouse           | eL:                                                    |         |                 | M :         | R:      |      |   |  |  |  |

| >               |                                                        |         |                 |             |         |      |   |  |  |  |

Figure 1.1: Cadence *icfb* Window with CMOSP35 technology

In order to create a new library select the following menu options:

### Tools $\rightarrow$ Library Manager

From the *Library Manager* window it is possible to access all available libraries and to create new libraries. In order to create a new library:

### $\textit{File} \rightarrow \textit{New} \rightarrow \textit{Library}$

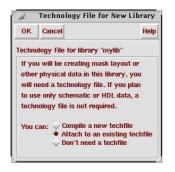

This will pop-up a new window where the library name can be specified. In this example we will use the name *mylib*.

Once you have entered the name of the library which is to be created, press *OK*. The next dialog will ask information about the technology file which is to be associated with the new library. For this tutorial we will be using CMOSP35, therefore, select *Attach to existing techfile*: this will bring another dialog window which lets us select which technology file we will use. Select *cmosp35*.

| Show Categories     Show Files       Jirrary     Cell     View       I     I       01ib     I       cells     alogLib       sic     sbefTechLib       osp35     naLlib       wLib     okage       dsp35     dsp35       dsp35     dsp35    <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I I<br>Olib<br>cells<br>alogLib<br>sic<br>suc<br>suc<br>suc<br>suc<br>suc<br>suc<br>suc<br>su                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 01ib<br>cells<br>alogLib<br>sic<br>sDefTechLib<br>sosp35<br>nalLib<br>wLib<br>ckage<br>dsp35<br>dsp35_dsm<br>ell<br>573p<br>11Lib<br>d773pn<br>2773pn<br>z773pn<br>ells_dsm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| cells<br>alogLib<br>sic<br>osp35<br>nalLib<br>wib<br>ckage<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp35<br>dsp36<br>dsp35<br>dsp36<br>dsp36<br>dsp35<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>dsp36<br>d |

| Aessages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

*Library* Dialog Window

Figure 1.2: Cadence Library Manager

Figure 1.4: Technology File For New Library Window

| S.      | Attac       | h Design | Library to Techno | ology File |

|---------|-------------|----------|-------------------|------------|

| ОК      | Cancel      | Defaults | Apply             | Help       |

| New De: | sign Librar | Ŷ        | mylib             |            |

| Tochnok | ogy Library |          | cmosp35           | =1         |

Figure 1.5: Attach Design Library Window

### **1.3** Schematic Capture

In this section we will be showing step by step how to enter a circuit schematic into Cadence's *Virtuoso Schematic Editor* and how to create a symbol view for the schematic using the *Virtuoso Symbol Editor*. This section will not give a circuit directly, but rather leave the reader to use some of the schematics presented later in the document (Section 1.4 is a good starting circuit for a novice user).

In order to create a new *Cell View*, open the *Library Manager* and click on the new library which has been created, followed by:

### $File \rightarrow New \rightarrow Cell \ View$

A dialog window will appear asking for the name of the new *Cell View*: enter OpAmp. This will automatically open the schematic capture session.

### 1.3.1 Virtuoso Schematic Editor

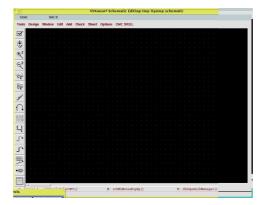

Figure 1.6) is the main window from which all of the schematic capture is performed. Along the left boarder of the window are icon-buttons which allow for easy access to the more common commands. Moving the mouse cursor over these windows will show a *tool-tip* which explains which command is executed with each button. All commands are also available via the menus at the top of the window. Most commands will also have a short-cut key associated with them.

When a schematic is entered the Insert Instance but is used (alternatively  $Add \rightarrow Instance$  may be used) is used in order to place components into the schematic. We will mostly be using transistors, resistors and capacitors (which are found in the library cmosp35) and power supplies and grounds (which are found in the library analogLib). If the exact name of the desired cell is not known the Browse button may be used to open the Library Manager and graphically select the component. Components are connected with narrow wires which may also be added via the icon-buttons or the menus.

When an instance of a component is added to a schematic all of the available parameters to the model may be set. These parameters may be changed later using the *Properties* option. Some parameters are mandatory to be entered (e.g. power supply voltage) whereas some parameters will default to certain values if they are not entered. Values may also be set to variables, by entering a string instead of a numeric value, which can be set

Figure 1.6: Cadence Virtuoso Schematic Editor

in the simulation stage.

Once a design has been entered, it can be saved with a *Check and Save* icon-button. This will do a general check of the circuit in order to make sure that all circuits have and ground and that all device terminals are connected to something.

An example of schematics for generating the characteristic curves is shown in Section 1.4. We will not discuss all of the options available for this window since they are very numerous and are mostly self-explanatory.

### 1.3.2 Virtuoso Symbol Editor

Once the schematic for the circuit is done, a symbol view must be created. This is the view which is used when an instance of the circuit is put into another schematic (e.g. a test bench circuit). Create a "default symbol" by clicking:

### $Design ightarrow Create \ Cell \ View ightarrow From \ Cell \ View$

Simply except the defaults and this opens the Symbol Editor. On startup the symbol editor will have a plain looking rectangle with terminal pins for each I/O pin inserted in the schematic. Once again we will simply accept the defaults and

In order to use the circuit which has been created is it necessary to create a test bench circuit. This test bench circuit is created similarly to the original circuit, except that no symbol is generally required. The symbol of the newly created circuit may be inserted as any other sub-circuit.

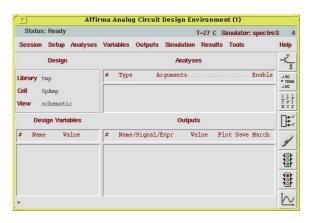

### 1.3.3 Affirma Analog Circuit Design Environment

Once a test bench circuit has been created and saved it is possible to start the simulation environment:

### $Tools \rightarrow Analog \ Environment$

The Affirma window, figure 1.7, is the window from which all simulations are configured and executed.

Figure 1.7: Affirma Analog Environment Simulation Window

In order to run a simulation there are several things which must be defined:

- Selecting a simulator. The Avant Star-HSPICE simulator is the best simulator available; in order to select the simulator: Setup → Simulator. In the dialog window which appears change the simulator selection to hspiceS; click OK. It is also important to define the environment for the simulator so that all of the correct models files are used by the simulator: Setup → Environment. The dialog box which appears contains a field entitled Include File. Set this field to /CMC/kits/cmosp35/models/hspice/icdhspice.init,click OK.

- Setting variables from the schematic. If there are any parameter settings which are set to variables, these variables must be copied from the cell view to the analog environment: Variables → Copy From Cell view. All variables which appear in the cell view will now be listed in the bottom left of the Affirma window. By double-clicking the variables it is possible to change the value of the variable for the next simulation run. All variables must be assigned values before a simulation may be performed.

- Selecting and configuring the simulations. There are several types of simulations which may be performed at the same time. In order to choose the simulation settings: Simulation → Choose. Most of the parameters available in the simulation settings are relatively straight forward and are left to the reader to lookup.

- Selecting which variables are saved/plotted from the simulation. The last step required to run a simulation is to set which variables should be plotted and saved. By default not all variables are saved since this could lead to vary large amounts a data being generated by the simulation, this becomes more important for larger designs. In order to plot/save a set of values:  $Outputs \rightarrow To \ Be \ Plotted \rightarrow Select \ on \ Schematic.$  This allows the user to click on all nodes (voltages) and device terminals (currents entering/leaving) in the schematic. The schematic should reflect which nodes/terminals have been selected. Once the selection is done press ESC.

Simulation may now be started by using the menu system or with the icon-buttons located on the right side of the *Affirma* window.

### 1.3.4 The Waveform Window

Once the simulation is complete all outputs which were selected to be plotted, will be in *Waveform Window*, Figure 1.8.

Figure 1.8: Waveform Window

The *Waveform Window* allows may customizations in order to generate desired plots; it is possible to add annotations, titles, modify plot ranges & axis and add additional plots. Most of these options are fairly straight

forward and will not be discussed in detail, the reader is encouraged to experiment with the various display options.

One of the more advanced features available from the window is the calculator which is discussed in the next section.

### 1.3.5 The Cadence Calculator

The Cadence *Calculator* is an extremely powerful tool for analyzing data generated by the simulation. Some of the many features of the *Calculator* are: basic arithmetic operations on waveforms, Discrete Fourier Transforms, Total Harmonic Distortion analysis, and many more.

| <u>v</u>  |         |        |          |        | с    | alcula | tor  |        |       |          |          |      |

|-----------|---------|--------|----------|--------|------|--------|------|--------|-------|----------|----------|------|

| Mindow N  | 4emorie | es Con | nstants  | Option | IS   |        |      |        |       |          | Hel      | p    |

|           |         |        |          |        |      |        |      |        |       |          |          |      |

| valuate B | uffer 🗌 | l Di   | isplay S | tack 🗌 | ſ.   |        | 🔶 st | andard | ⇔ RF  |          |          |      |

| browser   | vt      | it     | lastx    | x<>y   | dwn  | up     | sto  | rcl    | Sp    | ecial Fi | inctions |      |

| wave      | vf      | if     | Cle      | ar     | cist | app    | sin  | asin   | mag   | In       | exp      | abs  |

| family    | VS      | is     | en       | ter    | undo | eex    | COS  | acos   | phase | log10    | 10**x    | int  |

| erplot    | vdc     | idc    | -        | 7      | 8    | 9      | tan  | atan   | real  | dB10     | y**x     | 1/x  |

| plot      | op      | opt    | •        | 4      | 5    | 6      | sinh | asinh  | imag  | dB20     | x**2     | sqrt |

| printvs   | vn      | var    | •        | 1      | 2    | 3      | cosh | acosh  | 11    | fZ       | 13       | 14   |

| print     | mp      |        | 1        | 0      | [    | +/-    | tanh | atanh  |       |          |          |      |

Figure 1.9: Cadence Calculator

The calculator allows entry of waveform information by a variety of ways. One way of easily accessing the data is to use the *wave* button and followed by selecting one of the waveform's displayed in the *waveform window*. If the simulation contains a larger number of simulated values than the *browser* button may be employed to browse through all of the information stored from the simulation.

The order in which operations are entered into the calculator may be counter intuitive to new users: The calculator uses a Postfix notation. The table below shows some examples of the default order of operations:

| a+b               | a, b, +                     |

|-------------------|-----------------------------|

| a * b + c         | a, b, *, c, +               |

| $\sin a + \cos b$ | $b, \ cos, \ a, \ sin, \ +$ |

In the above table each letter represents one expression/waveform from the simulation. The *display stack* options is useful for evaluating large expressions. In order to learn more about the many functions available in the calculator the reader should refer to the Cadence documentation.

### 1.4 Generating the Characteristic MOSFET Curves

The enhancement-type MOSFET (Metal-Oxide Semiconductor Field-Effect Transistor) is the most widely used field-effect transistor in the FET family, which significance is on par with that of the bipolar junction transistor, with each having its own areas of application. The current-control mechanism is based on an electric field established by the voltage applied to the control terminal. And the current is conducted by only type of carrier(electrons or holes) depending on the type of FET (N channel or P channel).

#### 1.4.1 N-channel Enhancement-Type MOSFET

The transistor is fabricated on a P-type substrate, which is a single-crystal silicon wafer that provides physical support for the device. Two heavily doped n-type regions, the source and the drain regions, are created in the substrate. A thin (about 0.1um) layer of silicon dioxide(SiO2) is grown on the surface of the substrate, covering the area between the source the drain regions. Metal is deposited on top of the oxide layer to form the gate electrode of the device. Metal contacts are also made to the source region, the drain region, and the substrate, also known as the body. Thus, four terminals are brought out: the Gate(G), the Source(S), the Drain(D), and the Body(B).

Observe that the substrate forms PN junctions with the source and drain regions. In normal operation these PN junctions are kept reverse-biased at all time. Since the drain will be at a positive voltage relative to the source, the two PN junctions can be effectively cut off by simply connecting the substrate terminal to the source terminal.Here, the substrate will be considered as having no effect on device operation, and the MOSFET will be treated as a 3-terminal device, with the terminals being the gate(G), the source(S), and the drain(D). We applied a voltage to the gate controls current flow between source and drain. This current will flow in the longitudinal direction from drain to source in the region called "channel region". Note that this region has a length L and a width W, two important parameters of the MOSFET. Typically, L is in the range 1 to 10  $\mu m$ , and W is in the range 2 to 500  $\mu m$ .

The operation with  $V_{ds}$

With no bias voltage applied to the gate, two back-to-back diodes exist in series between drain and source. They prevent current conduction from drain to source when a voltage  $V_{ds}$  is applied. In fact, the path between drain and source has a very high resistance (of the order of  $10^{12} \Omega$ ) With a positive voltage, which exceed the threshold voltage  $V_t$ , applied to the gate, the transistor induced a n-channel. When applying a positive voltage  $V_{ds}$  between drain and source, as shown in the figure below,

iD-vDS-vGS characteristics of P-channel MOSFET

Figure 1.10: N-Channel Test Circuit

The voltage  $V_{ds}$  cause a current  $i_D$  to flow through the induced N channel. Current is carried by free electrons travelling from source to drain. The magnitude of  $i_D$  depends on the density of electrons in the channel, which in turn depends on the magnitude of  $V_{GS}$ . As  $V_{GS}$  exceeds  $V_t$ , more electrons are attracted into the channel. We may visualize the increase in charge carriers in the channel as an increase in the channel depth. The result is a channel of increased conductance or equivalently reduced resistance.

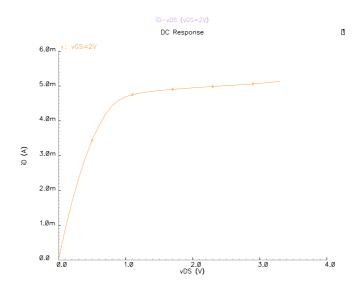

Let  $V_{GS}$  be held constant at a value greater than  $V_t$  (for example 2V), and increase the  $V_{DS}$  from 0 to 3.3V. As  $V_{DS}$  is increased, the  $I_D - V_{DS}$ curve is shown in

Eventually, when  $V_{DS}$  is increased to the value that reduces the voltage between gate and channel at the drain end to  $V_t$ , that is :

$V_{GS} - V_{DS} = V_t$

or

$$V_{DS} = V_{GS} - V_t$$

the channel depth at the drain end decreases to almost zero, and the channel is said to be pinched off. Increase  $V_{DS}$  beyond this value has little effect (theoretically, no effect) on the channel shape, and the current through the channel remain constant at the value reached for  $V_{DS} = V_{GS} - V_t$ . The drain current thus saturates at this value, and the MOSFET is said to

Figure 1.11:  $I_D - V_{DS}$  Curve

have entered the saturation region of operation. The voltage  $V_{DS}$  at which saturation occurs is named  $V_{DS,sat}$

$$V_{DS,sat} = V_{GS} - V_t$$

Obviously, for every value of  $V_{GS} \geq V_t$ , there is a corresponding value of  $V_{DS,sat}$ . The device operates in the saturation region if  $V_{DS} \geq V_{DS,sat}$ . The region of the  $I_D - V_{DS}$  characteristic obtained for  $V_{DS} < V_{DS}$ ,sat is called the triode region.

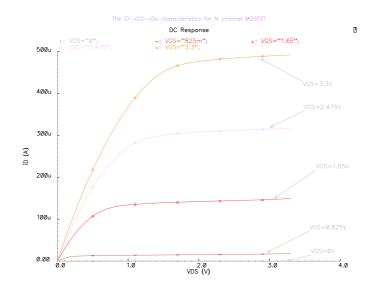

The  $I_D - V_{DS}$  Characteristics

The Figure above shows a typical set of  $I_D - V_{DS}$  characteristics, which are a family of curves, each measured at a constant  $V_{GS}$ . We can see that there are three distinct regions of operation: the cutoff region, the triode region, and the saturation region. The saturation region is used if the FET is to operate as a amplifier. For operation as a switch, the cutoff and triode regions are utilized.

### 1. Triode

If  $V_{GS} > V_t$  and  $V_{DS} \leq V_{GS} - V_t$ , then the n-channel is continuous all the way from S to D. The S and D are connected by a conductor (or a resistor) of a given resistance. The drain current increases if the voltage drop between S and D increases. The channel resistance

Figure 1.12:  $I_D - V_{DS}$  Curve

depends on how much charge is injected at the S-end, which in turn is controlled by  $v_{GS}$ . The Drain current  $I_d$  depends on both  $v_{GS}$  and  $V_{GD}$  (or  $V_{DS}$ ). The  $I_D - V_{DS}$  characteristics can be approximately described by the relationship

$$I_D = K \left[ 2(V_{GS} - V_t) V_{DS} - V_{DS} \cdot V_{DS} \right]$$

(1.2)

in which K is a device parameter given by

$$K = 0.5U_n \cdot C_{ox} \left(\frac{W}{L}\right) \quad \left[\frac{A}{V^2}\right] \tag{1.3}$$

$U_n$  physical constant known as the electron mobility (its value in this case applies for the electrons in the induced n channel)

$C_{ox}$  oxide capacitance, the capacitance per unit area of the gate-to-body capacitor for which the oxide layer serves as dielectric.

L,W the length and the width of the channel.

Since for a given fabrication process the quantity  $(0.5U_n^*C_{ox})$  is a constant, approximately  $10\mu A/V^2$  for the standard NMOS process with a  $0.1\mu m$  oxide thickness. So the aspect ratio of  $\frac{W}{L}$  determines its conductivity parameter K.

If  $V_{DS}$  is sufficiently small so that we can neglect the  $V_{DS} \cdot V_{DS}$  in equation 1.2, then the  $I_D - V_{DS}$  characteristics near the origin the relationship

$$I_D \cong 2K(V_{GS} - V_t)V_{DS} \tag{1.4}$$

This linear relationship represents the operation of the MOS transistor as a linear resistance  $R_{DS}$

$$R_{DS} = \frac{V_{DS}}{I_D} = \frac{1}{2K(V_{GS} - V_t)}$$

(1.5)

### 2. Saturation

If  $V_{GS} > V_t$  and  $V_{DS} \ge V_{GS} - V_t$ , then N-channel is induced at the Send, but the channel is depleted at the D-end. That is, the N-channel is pinched off at the Drain-end. Increasing  $V_{ds}$  beyond  $V_{ds-(sat)}$ , or equivalently decreasing  $V_{GD}$  below  $V_t$ , creates a fully depleted region between the inversion n-channel and the drain region. An electric field is set up in this region, pointing from the Drain region toward the inversion channel. Carrier electrons in the N-channel that reach the depletion boundary are swept across the depletion region into the Drain. This is similar to PN junction diode where the minority carrier electrons of the P-side are swept to the n-side by the built-in field whenever they reach the depletion boundary. Once the drain-end of channel is pinched off, the current no longer depends on the voltage apply between S and D.

The boundary between the triode region and the saturation region is characterized by

$$V_{DS} = V_{GS} - V_t \tag{1.6}$$

Substituting it into Equation 1.2 gives the saturation value of the current  $I_D$  is

$$I_D = K(V_{GS} - V_t) \cdot (V_{GS} - V_t)$$

(1.7)

Thus in saturation the MOSFET provides a drain current whose value is independent of the drain voltage  $V_{DS}$  and is determined by the gate voltage  $V_{GS}$  according to the square-law relationship.

The complete independence of  $I_D$  on  $V_{DS}$  in saturation and the corresponding infinite output resistance at the drain is an idealization based on the premise that once the channel is pinched off at the drain end, further increases in  $V_{DS}$  have no effect on the channel's shape. In practice, increasing  $V_{DS}$  beyond  $v_{DS}$ , sat does affect the channel somewhat.

Specifically, as  $V_{DS}$  is increased, the channel pinch-off point is moved slightly away from the drain toward the source. Thus the effective channel is reduced, a phenomenon called channel-length modulation. Since the channel resistance is proportional to the channel length, the channel resistance is decreased. This results in the slight increase of the drain current beyond the saturation level. Now since K is inversely proportional to the channel length (Equation 1.3), so, K and, correspondingly,  $I_D$ , increases with  $V_{DS}$ . Mathematically, the channel length modulation introduces a  $V_{DS}$ -dependent term in  $I_D$ :

$$I_D = K(V_{GS} - V_t)(V_{GS} - V_t)(1 + \lambda \cdot V_{DS})$$

(1.8)

$\lambda$  the channel-length modulation parameter:  $0.005 < \lambda < 0.03$

From Fig.nid.ps we extrapolated the straight-line  $I_D - V_{DS}$  characteristics in saturation, intercept the  $V_{DS}$ -axis at the point  $V_{DS} = \frac{-1}{\lambda} = -V_A$ . So  $v_A$  is in the range 200 to 30 volts. It should be obvious that channel-length modulation makes the output resistance in saturation finite. Let the output resistance Rout as

$$R_{out} = \frac{1}{\lambda \cdot K(V_{GS} - V_t) \cdot (V_{GS} - V_t)} \qquad V_{GS} = constant \qquad (1.9)$$

approximated by

$$R_{out} \cong \frac{1}{\lambda \cdot I_D} \tag{1.10}$$

substituted by  $\lambda = \frac{1}{V_A}$

$$R_{out} \cong \frac{V_A}{I_D} \tag{1.11}$$

Thus the output resistance is inversely proportional to the DC bias current  $I_D$ .

3. Cutoff

If  $V_{GS} < V_t$  (and of course,  $V_{GD} < V_t$ ), then the no n-channel is present and no current flows.

### 1.4.2 P-channel Enhancement-Type MOSFET

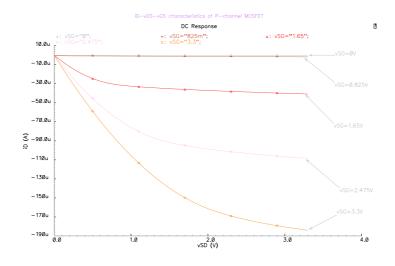

A P-channel enhancement-type MOSFET (PMOS transistor) is fabricated on an N-type substrate with p+ regions for the drain and the source, and holes as charge carriers. The device operates in the same manner as the N-channel device except the  $V_{GS}$  and  $V_{DS}$  are negative and the threshold

iD-vDS-vGS characteristics of P-channel MOSFET

Figure 1.13: P-Channel Test Circuit

voltage  $V_t$  is negative. Also the current  $i_D$  enters the source terminal and leaves through the drain terminal.

To induce a channel we apply a gate voltage that is more negative than  $V_t$ , and apply a drain voltage that is more negative than the source voltage (i.e.  $V_{DS}$  is negative or, equivalently,  $v_{SD}$  is positive). The current  $i_D$  is given by the same equation as for NMOS, and the K is given by

$$K = 0.5 \cdot U_p \cdot C_{ox} \left(\frac{W}{L}\right) \tag{1.12}$$

where  $U_p$  is the mobility of holes in the induced p channel. Typically,  $U_p \cong 0.5U_n$ , with the result that for the same W/L ratio a PMOS transistor has half the value of K as the NMOS device.

The  $I_D - V_{DS}$  characteristics is shown above. The current  $I_D$  is given by the same equation used for NMOS.

$$I_D = K(V_{GS} - V_t)(V_{GS} - V_t)(1 + \lambda \cdot V_{DS})$$

where  $V_{GS}$ ,  $V_t$ ,  $\lambda$ , and  $V_{DS}$  are all negative.

PMOS technology was originally the dominant one. However, because NMOS devices can be made smaller and thus operate faster, and because NMOS requires lower supply voltages than PMOS, NMOS technology has virtually replaced PMOS. Nevertheless, it is important to develop the PMOS

Figure 1.14:  $I_D - V_{DS}$  Curve

transistor for two reasons: PMOS devices are still available for discretecircuit design, and more importantly, both PMOS and NMOS transistors are utilized in CMOS circuits!

### Chapter 2

### An Introduction to Op-Amps

### 2.1 Parameters of an Op-Amp

This section will discuss Op-Amp parameters. The designer of an Op-Amp must have a clear understanding of what Op-Amp parameters mean and their impact on circuit design. The selection of any Op-Amp must be based on an understanding of what particular parameters are most important to the application. In the next section, we will discuss the method of measurement of these different parameters

### 2.1.1 Offset Voltage

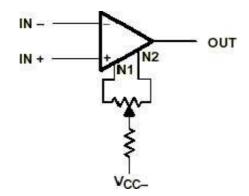

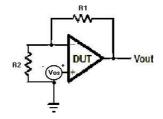

All Op-Amps require a small voltage between their inverting and noninverting inputs to balance mismatches due to unavoidable process variations. The required voltage is known as the input offset voltage and is abbreviated  $V_{os}$ .  $V_{os}$  is normally modelled as a voltage source driving the noninverting input. Generally, Bipolar input Op-Amps typically offer better offset parameters than JFET or CMOS input Op-Amps. There are two other parameters related to and affect  $V_{os}$ : the average temperature coefficient of input offset voltage, and the input offset voltage long-term drift. The average temperature coefficient of input offset voltage, a  $V_{os}$ , specifies the expected input offset drift over temperature. Its units is  $\left[\frac{mV}{oC}\right]$ .  $V_{os}$  is measured at the temperature extremes of the part, and a  $V_{os}$  is computed as  $\frac{V_{os}}{oC}$ . Normal aging in semiconductors causes changes in the characteristics of devices. The input offset voltage long-term drift specifies how  $V_{os}$  is expected to change with time. Its units are  $\frac{mV}{month}$ . Input offset voltage is of concern anytime that DC accuracy is required of the circuit. One way to null the offset is to use external null inputs on a single Op-Amp package (2.1). A potentiometer is

Figure 2.1: Offset Voltage Adjust

connected between the null inputs with the adjustable terminal connected to the negative supply through a series resistor. The input offset voltage is nulled by shorting the inputs and adjusting the potentiometer until the output is zero. However, even if the  $V_{os}$  is nulled at the beginning, it will change with temperature and some other conditions.

#### 2.1.2 Input Current

The input circuitry of all Op-Amps requires a certain amount of bias current for proper operation. The input bias current,  $I_{IB}$ , is computed as the average of the two inputs:

$$I_{IB} = \frac{(I_N + I_P)}{2}$$

(2.1)

CMOS and JFET inputs offer much lower input current than standard bipolar inputs. The difference between the bias currents at the inverting and noninverting inputs is called the input offset current,  $I_{os} = I_N + I_P$ . Offset current is typically an order of magnitude less than bias current.

Input bias current is of concern when the source impedance is high. If the Op-Amp has high input bias current, it will load the source and a lower than expected voltage is seen. The best solution is to use an Op-Amp with either CMOS or JFET input. The source impedance can also be lowered by using a buffer stage to drive the Op-Amp that has high input bias current. In the case of bipolar inputs, offset current can be nullified by matching the impedance seen at the inputs. In the case of CMOS or JFET inputs, the offset current is usually not an issue and matching the impedance is not necessary. The average temperature coefficient of input offset current,

Figure 2.2: Output Voltage Swing

$I_{os}$ , specifies the expected input offset drift over temperature. Its units are  $\left[\frac{mA}{oC}\right]$ .

### 2.1.3 Input Common Mode Voltage Range

The input common voltage is defined as the average voltage at the inverting and noninverting input pins. If the common mode voltage gets too high or too low, the inputs will shut down and proper operation ceases. The common mode input voltage range, VICR, specifies the range over which normal operation is guaranteed. For instance, Rail to rail input Op-Amps use complementary N and P channel devices in the differential inputs. When the common-mode input voltage nears either rail, at least one of the differential inputs is still active, and the common-mode input voltage range includes both power rails.

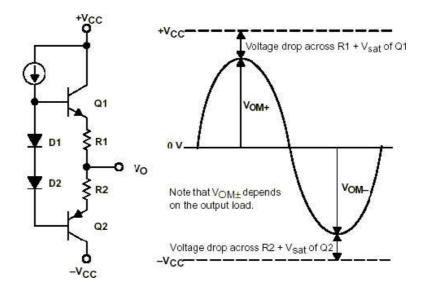

### 2.1.4 Maximum Output Voltage Swing

The maximum output voltage,  $V_{OM}$ , is defined as the maximum positive or negative peak output voltage that can be obtained without waveform clipping, when quiescent DC output voltage is zero.  $V_{OM}$  is limited by the output impedance of the amplifier, the saturation voltage of the output transistors, and the power supply voltages. This is shown pictorially in 2.2. This emitter follower structure cannot drive the output voltage to either rail. Rail-to-rail output Op-Amps use a common emitter (bipolar) or common source (CMOS) output stage. With these structures, the output voltage swing is only limited by the saturation voltage (bipolar) or the on resistance (CMOS) of the output transistors, and the load being driven.

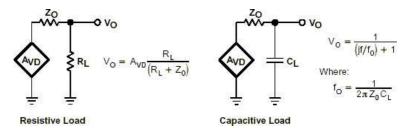

### 2.1.5 Output Impedance

Different data sheets list the output impedance under two different conditions. Some data sheets list closed-loop output impedance while others list open-loop output impedance, both designated by  $Z_o$ .  $Z_o$  is defined as the small signal impedance between the output terminal and ground. Generally, values run from 50 to  $200\Omega$ .

Common emitter (bipolar) and common source (CMOS) output stages used in rail-to-rail output Op-Amps have higher output impedance than emitter follower output stages. Output impedance is a design issue when using rail-to-rail output Op-Amps to drive small resistive or large capacitive loads. If the load is mainly resistive, the output impedance will limit how close to the rails the output can go. If the load is capacitive, the extra phase shift will erode phase margin. 2.3 shows how output impedance affects the output signal assuming  $Z_o$  is mostly resistive.

Figure 2.3: Effect of Output Impedance

### 2.1.6 Common-Mode Rejection Ratio

Common-mode rejection ratio, CMRR, is defined as the ratio of the differential voltage amplification to the common-mode voltage amplification,  $\frac{A_{dif}}{A_{com}}$ . Ideally this ratio would be infinite with common mode voltages being totally rejected.

The common-mode input voltage affects the bias point of the input differential pair. Because of the inherent mismatches in the input circuitry, changing the bias point changes the offset voltage, which, in turn, changes the output voltage.

### 2.1.7 Supply Voltage Rejection Ratio

Supply voltage rejection ratio, kSVR (AKA power supply rejection ratio, PSRR), is the ratio of power supply voltage change to output voltage change.

The power voltage affects the bias point of the input differential pair. Because of the inherent mismatches in the input circuitry, changing the bias point changes the offset voltage, which, in turn, changes the output voltage.

For a dual supply Op-Amp,  $KSVR = \frac{VCC}{VOS}$  or  $KSVR = \frac{V_{DD}}{VOS}$ . The term  $V_{CC}$  means that the plus and minus power supplies are changed symmetrically. For a single supply Op-Amp,  $KSVR = \frac{VCC}{VOS}$  or  $KSVR = \frac{V_{DD}}{VOS}$ . Also note that the mechanism that produces kSVR is the same as for CMRR. Therefore kSVR as published in the data sheet is a DC parameter like CMRR. When kSVR is graphed vs. frequency, it falls off as the frequency increases.

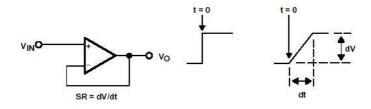

### 2.1.8 Slew Rate

Slew rate, SR, is the rate of change in the output voltage caused by a step input. Its units are V/ms or V/ms. 2.4 shows slew rate graphically.

Figure 2.4: Slew Rate

The primary factor controlling slew rate in most amps is an internal compensation capacitor CC, which is added to make the Op-Amp unity gain stable. Referring to 2.5, voltage change in the second stage is limited by the charging and discharging of the compensation capacitor CC. The maximum rate of change is when either side of the differential pair is conducting 2IE. Essentially  $SR = \frac{2IE}{CC}$ . However, that not all Op-Amps have compensation capacitors. In Op-Amps without internal compensation capacitors, the slew rate is determined by internal Op-Amp parasitic capacitances. Uncompensated Op-Amps have greater bandwidth and slew rate, but the designer must ensure the stability of the circuit.

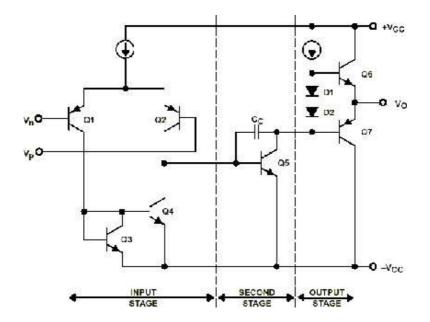

Figure 2.5: Op amp schematic simplified

In Op-Amps, power consumption is traded for noise and speed. In order to increase slew rate, the bias currents within the Op-Amp are increased.

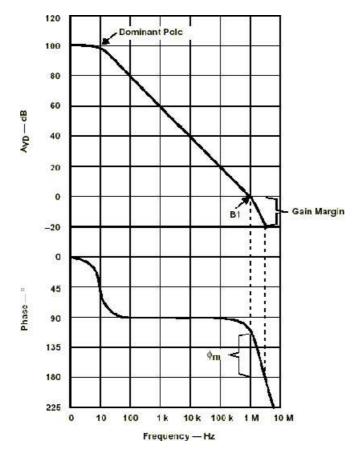

### 2.1.9 Unity Gain Bandwidth and Phase Margin

Unity-gain bandwidth (B1) and gain bandwidth product (GBW) are very similar. B1 specifies the frequency at which  $A_{VD}$  of the Op-Amp is 1. GBW specifies the gain-bandwidth product of the Op-Amp in an open loop configuration and the output loaded:

$$GBW = AVD \cdot f \tag{2.2}$$

Phase margin at unity gain (fm) is the difference between the amount of phase shift a signal experiences through the Op-Amp at unity gain and  $180^{\circ}$ :

$$fm = 180^o - f@B1 \tag{2.3}$$

Gain margin is the difference between unity gain and the gain at  $180^{\circ}$  phase shift:

$$Gain margin = 1 - Gain@180^{\circ} phase shift$$

(2.4)

In order to make the Op-Amp stable, a capacitor,  $C_C$ , is purposely fabricated on chip in the second stage (2.5). This type of frequency compensation is termed dominant pole compensation. The idea is to cause the open-loop gain of the Op-Amp to roll off to unity before the output phase shifts by 180°. 2.5 is very simplified, and there are other frequency shaping elements within a real Op-Amp. 2.6 shows a typical gain vs. frequency plot for an internally compensated Op-Amp.

Figure 2.6: Voltage Amplification and Phase Shift vs. Frequency

Phase margin and gain margin are different ways of specifying the stability of the circuit. Since rail-to-rail output Op-Amps have higher output impedance, a significant phase shift is seen when driving capacitive loads. This extra phase shift erodes the phase margin, and for this reason most CMOS Op-Amps with rail-to-rail outputs have limited ability to drive capacitive loads.

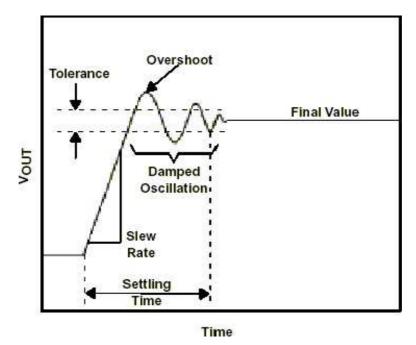

### 2.1.10 Settling Time

It takes a finite time for a signal to propagate through the internal circuitry of an Op-Amp. Therefore, it takes a period of time for the output to react to a step change in the input. In addition, the output normally overshoots the target value, experiences damped oscillation, and settles to a final value. Settling time,  $t_s$ , is the time required for the output voltage to settle to within a specified percentage of the final value given a step input. Settling time is a design issue in data acquisition circuits when signals are changing rapidly.

Figure 2.7: Settling Time

### 2.2 Methodology of Choosing Op-Amp Parameters

The methodology of choosing the parameters of the transistors, and their relationships, then it will be possible to get the desired quiescent point to ensure the ideal wave output.

Here we will to present a method of choosing the parameter in an Op-

Amp circuit, and in the same way we can get a very efficient optimization method. Further more in this way we can learn how to combine different parts of a circuit together, and deal with more complex circuits. First of all we must clarify the relationship among different parameters, then we can finish our job orderly. The quiescent point is very important for our design.

### 2.3 How to Adjust the Parameters

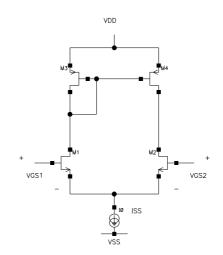

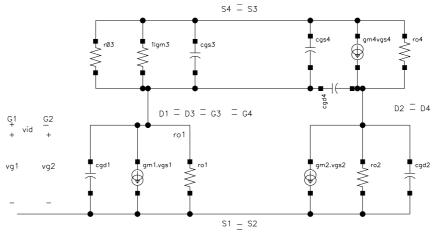

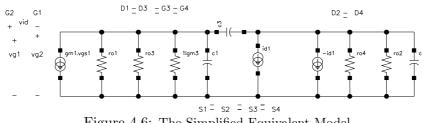

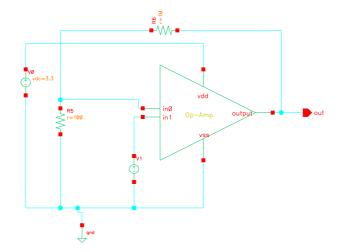

To simplify the discussion, we will concentrate on the simplest OTA Op-Amp 2.8 and demonstrate how to adjust its parameters to get the proper DC gain. At the same time we try to extend the method to other sophisticated architectures.

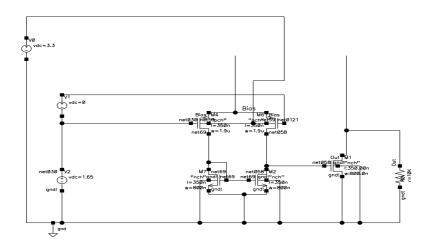

#### 2.3.1 Specification

Here we are asked to design an Op-Amp, whose  $V_{DD} = 3.3 V$ ,  $V_{SS} = 0 V$ , input bias voltage = 1.65V (Input  $V_0 = 1.65 V$ ). Swing of output (Considering the current source  $V_{DD}$  will occupy some voltage, the swing should be  $0 \rightarrow 3 V$ .)

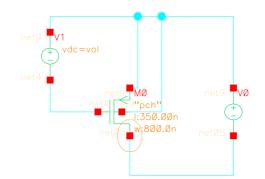

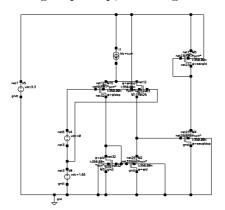

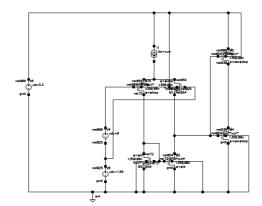

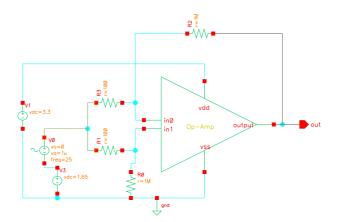

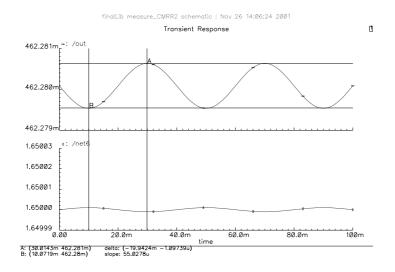

Figure 2.8: Circuit with Default Parameters

### 2.3.2 Procedure of Optimization

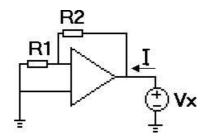

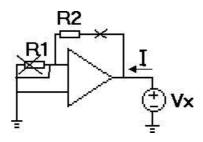

- 1. Draw a circuit with default parameters. (See Figure 2.8).

- 2. Adjust the current source value  $I_0$ . The current value takes highest priority of all of the parameters, all of the other parameters will be chosen to match the current value.

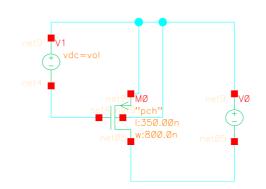

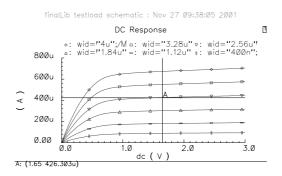

From the circuit, we know that when the Op-Amp is working in the common mode (which means the  $V_1 = V_0 = 1.65 V$ ), then the current through the two (2) differential amplifiers is symmetric, so the value of  $I_1 = \frac{1}{2} \cdot I_0$ .  $V_{out} = 1.65 V$ ,  $V_{ref} = 1.65 V$ , from here we can decide what is the maximum and minimum value we can get through a PMOS. We design a very simple circuit to test the current value from the drain of a PMOS (Figure 2.9). When changing the width of the channel of the PMOS, we can get a set of values of the current value of the drain(Figure 2.10). Considering the width of the active load should not to be too large so we can get better gain. The range of the length should be  $400nm \rightarrow 2000 nm$ , then  $I_1$  should be from  $86.4366\mu A \rightarrow 800.00\mu A$ . So the  $I_0$  should be double  $I_1$  it should be from  $170\mu A \rightarrow 1700\mu A$ .

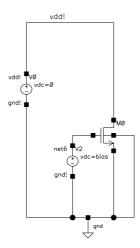

Figure 2.9: Simple Test Circuit for Drain Current

We can choose any value inside the range, so we regard the  $400\mu m$  as the initial value of our design.

- 3. Decide the width of the channel of the active load. From Figure 2.9 we perform a parametric analysis. The value of the width of the channel, through which we can get the proper value for the quiescent point. It is about  $1.25\mu m$ .

- 4. We can assign an arbitrary big value to the width of the differential

Figure 2.10: Simple Test Circuit - Parametric Analysis of Channel Width

amplifier, suppose we choose a value 5 times bigger than the width of the active load.

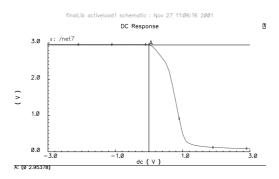

5. Do the simulation and compare the gain we get with the gain we want.

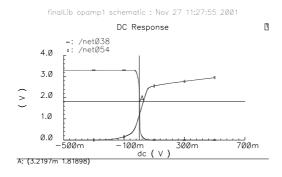

Figure 2.11: Simple Test Circuit - DC Response/Gain

### 2.3.3 Optimize the Parameters of the Op-Amp

1. According to the gain of the specification, decide the width of the differential amplifier.

$$G_m = \left(2K'_n I_0 \cdot \left(\frac{W}{L}\right)\right)^{\frac{1}{2}}$$

$$R_{out} = V_e \frac{L_1}{I_0}$$

$$A_V = G_m R_{out} = V_e \left( 2K'_n \frac{W_1 L_1}{I_0} \right)^{frac12}$$

There are three (3) variables that will affect  $A_V$ , W, L and  $I_0$ .

If there is small difference between the two (2) gains, then what we need to do is just to adjust the value of the length and the width of the channel of differential amplifier, otherwise we must reduce the  $I_0$ .

2. Reduce  $I_0$ ; according to the fabricating technology, the width of the channel of the transistor cannot be less than  $350\mu m$ , which means we cannot reduce the  $I_0$  less than  $170\mu A$ . As mentioned above, otherwise the quiescent point cannot be at the middle of the curve. (See Figure 2.12), this will distort the input waveform. Each time  $I_0$  is adjusted the width of the active load should be changed accordingly. Thus another way to adjust  $I_0$  must be devised.

Figure 2.12: Waveform Distortion

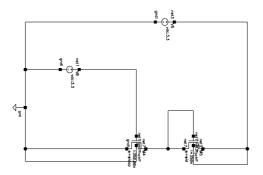

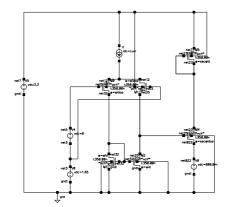

3. Further reducing  $I_0$ . First, we can cascade active loads together, because the voltage is on the cascade active load, there is less voltage across each transistor, so the  $I_0$  can be reduced dramatically. However, it becomes more complex to further optimize the circuit. See figure 2.13

Figure 2.13: Active Loads Cascaded Together

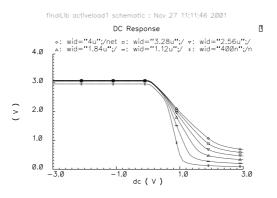

Figure 2.14: Cascaded Active Loads - DC Response/Gain

### CHAPTER 2. AN INTRODUCTION TO OP-AMPS

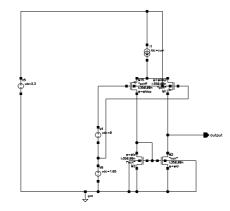

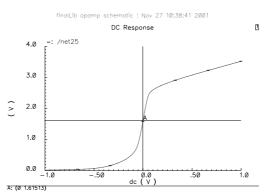

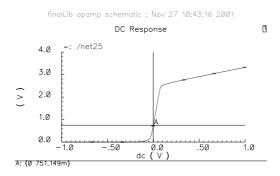

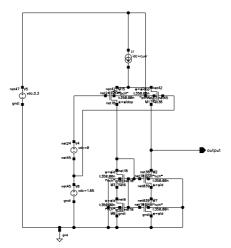

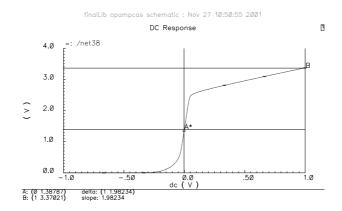

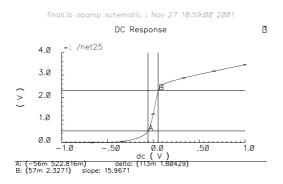

4. Cascade Op-Amp - adjusting the quiescent point: If after all of the above effort, we still cannot get the proper gain, we have to use a cascade Op-Amp. The key to optimizing the cascade Op-Amp is the quiescent point, which guarantees the proper operation of the circuit. Please refer the Figure 2.15 (Output curve of first the stage).

The output of the first stage is linear in the area of  $(0.5 V \rightarrow 2.15 V)$ . So we should adjust the quiescent point of the input of the second stage.

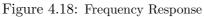

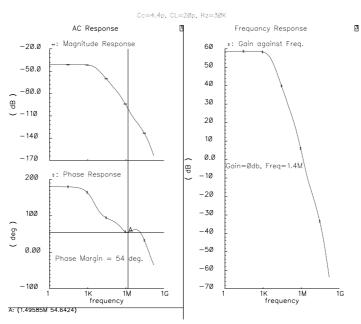

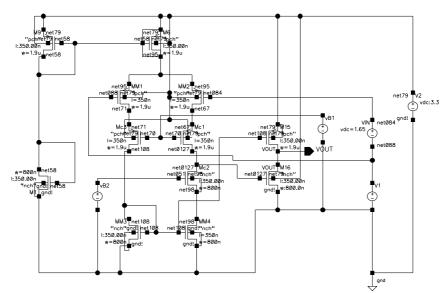

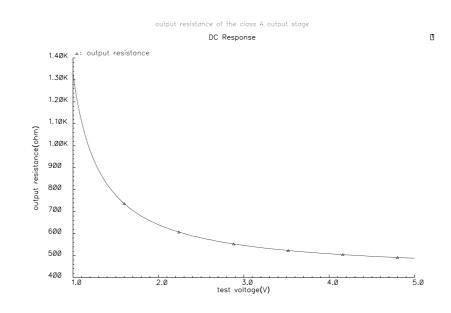

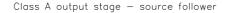

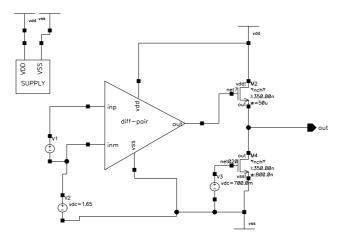

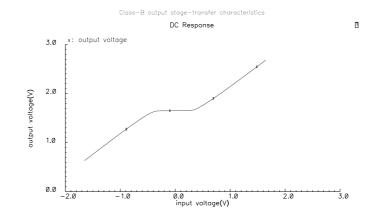

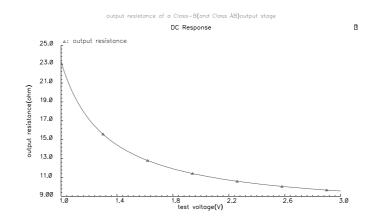

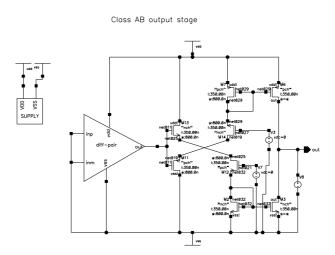

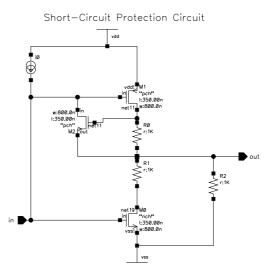

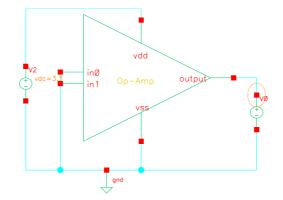

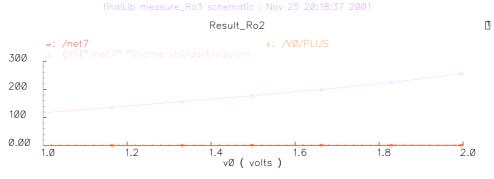

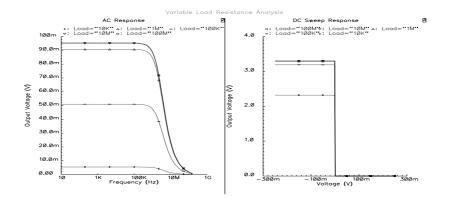

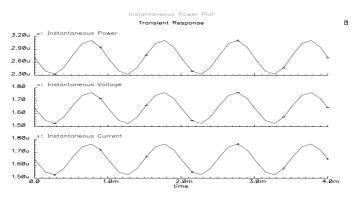

Checking the 2 stage Op-Amp, as in Figure 2.16