Ver 1.1

$\langle p \rangle$

# TFT LCD Specification

# Model NO.: TD028TTEB5

| Customer Signature |

|--------------------|

|                    |

| Date               |

|                    |

$\oslash$

#### Table of Contents

| NO. | Item                       | Page |

|-----|----------------------------|------|

|     | Cover Sheet                | 1    |

|     | Table of Contents          | 2    |

|     | Record of Reversion        | 3    |

| 1   | Features                   | 4    |

| 2   | General Specification      | 4    |

| 3   | Input / Output Terminals   | 5    |

| 4   | Absolute Maximum Ratings   | 7    |

| 5   | Electrical Characteristics | 8    |

| 6   | Block Diagram              | 10   |

| 7   | Timing Chart               | 11   |

| 8   | Power On/Off Sequence      | 22   |

| 9   | Optical Characteristics    | 23   |

| 10  | Reliability                | 27   |

| 11  | Handling Cautions          | 31   |

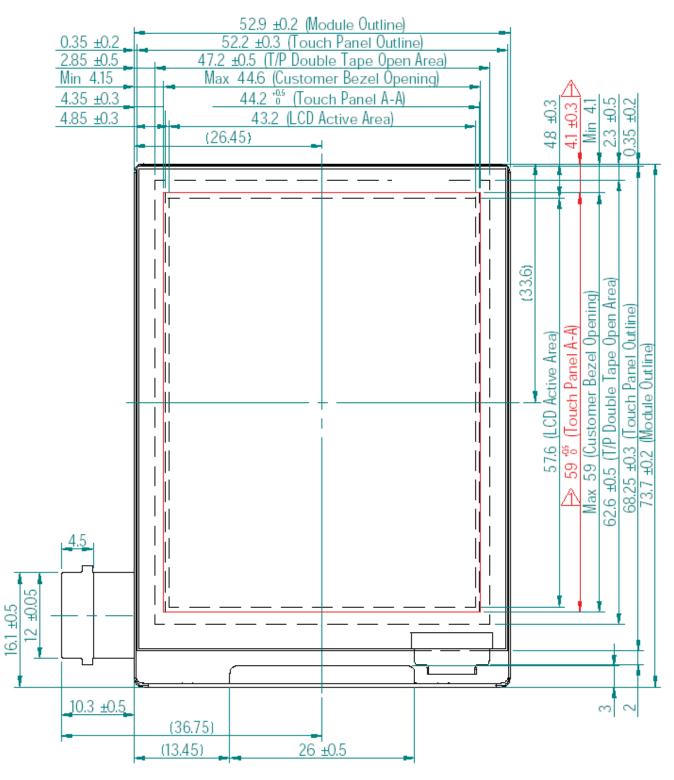

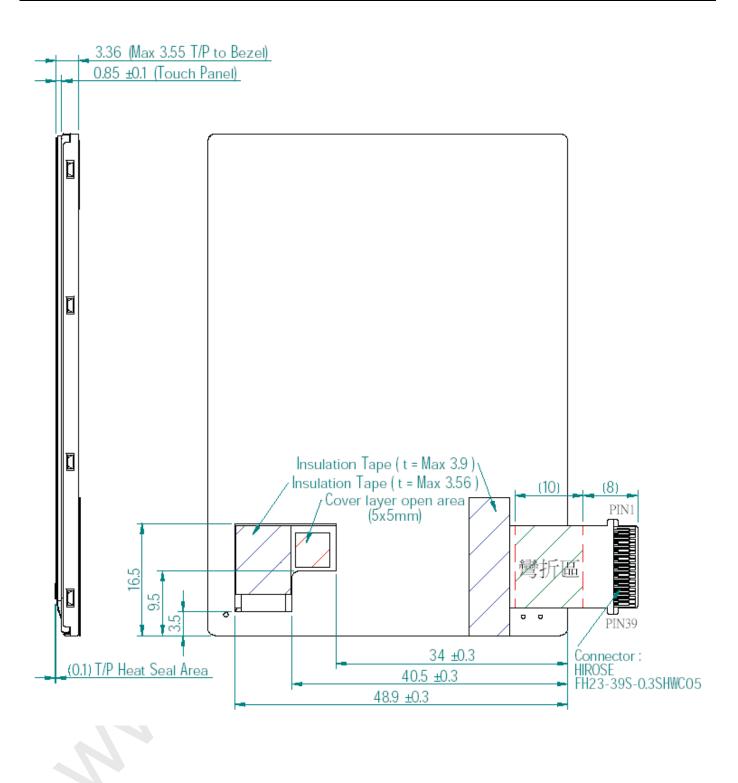

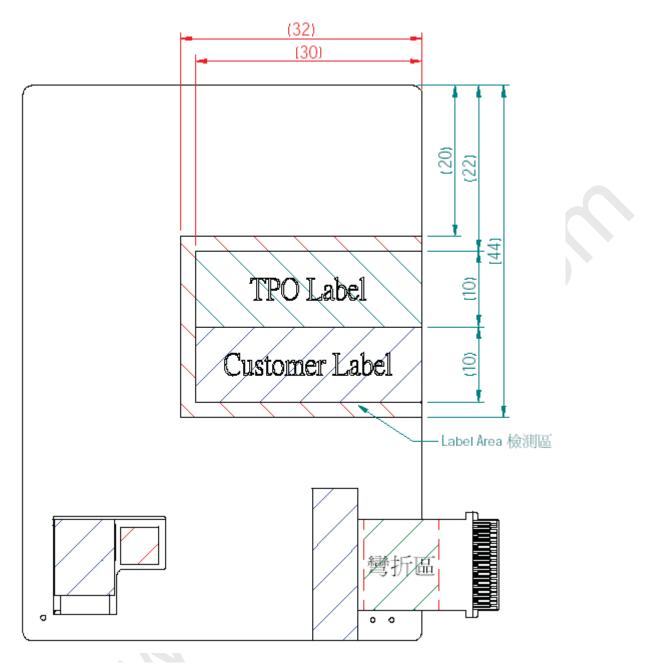

| 12  | Mechanical Drawing         | 34   |

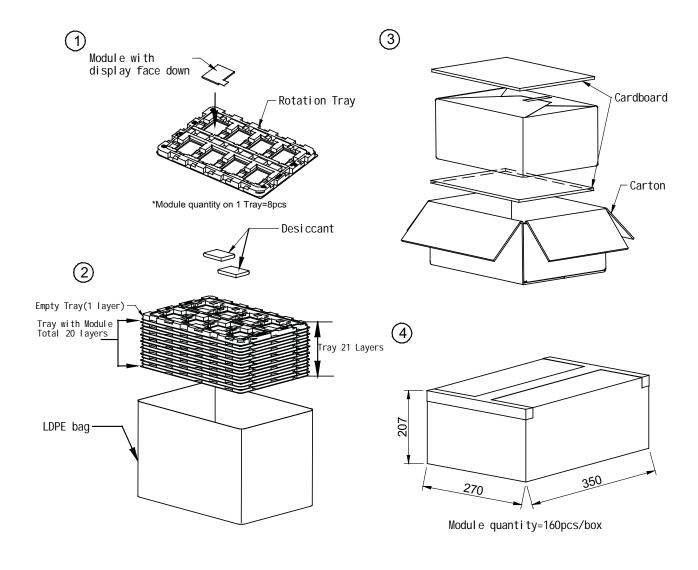

| 13  | Packing Drawing            | 37   |

|     |                            |      |

The information contained herein is the exclusive property of toppoly Optoelectronics corporation, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of toppoly Optoelectronics corporation.

$\oslash$

#### Record of Reversion

| Rev | Issued Date   | Description                       |

|-----|---------------|-----------------------------------|

| 0.0 | Nov, 10, 2006 | New Create                        |

| 0.1 | Nov, 23, 2006 | Update RA SPEC                    |

| 1.0 | DEC, 15, 2006 | Apply for system                  |

|     |               | Update White Chromaticity         |

|     |               | Update DVDD/AVDD Supply Current   |

| 1.1 | Mar, 18, 2007 | Update Reliability SPEC, item 10. |

The information contained herein is the exclusive property of toppoly Optoelectronics corporation, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of toppoly Optoelectronics corporation.

$\langle P \rangle$

#### 1. FEATURES

The 2.8 inch (real 2.83 inch) LCD module is the Transmissive active matrix color TFT LCD module. LTPS (Low Temperature Poly Silicon) TFT technology is used and COG design are built on the panel. Highly integrated LCD module includes backlight and TFT LCD panel with minimal external circuits and components required.

#### 2. GENERAL SPECIFICATION

| Ι                       | tem                   | Description                       | Unit     |

|-------------------------|-----------------------|-----------------------------------|----------|

| Display Size (Diagonal) |                       | 2.8 inch (real 2.83 inch)         | -        |

| Display Type            |                       | Transmissive                      | -        |

| Active Area (HxV)       |                       | 43.2 X 57.6                       | mm       |

| Number of Dots (HxV)    |                       | 240 x RGB x 320                   | dot      |

| Dot Pitch (HxV)         |                       | 0.06 X 0.180                      | mm       |

| Color Arrangement       |                       | RGB Stripe                        | <u> </u> |

| Color Numbers           |                       | 262,144 (18 bits)                 | -        |

| Outline Dimension (Hx   | VxT)                  | 52.9x73.7x3.4 (TYP; FPC excluded) | mm       |

| Weight                  |                       | 45                                | g        |

| Power consumption       | LCD Panel +<br>System | 28                                | mW       |

| Fower consumption       | Backlight             | 288 (Typ, I⊧= 20mA)               | 111 VV   |

The information contained herein is the exclusive property of toppoly Optoelectronics corporation, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of toppoly Optoelectronics corporation.

屏库:全球液晶屏交易中心

### TD028TTEB5

$\oslash$

#### 3. INPUT/OUTPUT TERMINALS

3.1 TFT LCD module

Recommend connector: FH23-39S-0.3SHW(05)/HIROSE

| Pin | Symbol  | I/O | Description                            | Remark         |

|-----|---------|-----|----------------------------------------|----------------|

| 1   | LED+    | -   | High Voltage Power Supply for LED      |                |

| 2   | LED-    | -   | Low Voltage Power Supply for LED       |                |

| 3   | DVDD    | -   | Power Supply of Digital                |                |

| 4   | AVDD    | -   | Input to DC/DC                         |                |

| 5   | VSS     | -   | Ground                                 |                |

| 6   | YU      | -   | Touch Panel Y(12 Clock Side)           |                |

| 7   | XL      | -   | Touch Panel X(Left Side)               |                |

| 8   | YL      | -   | Touch Panel Y(6 Clock Side)            |                |

| 9   | XR      | -   | Touch Panel X(Right Side)              |                |

| 10  | CDI CC  | т   | CDI Chin Calast                        | Reserved for   |

| 10  | SPI_CS  | Ι   | SPI Chip Select                        | Register Setup |

| 11  |         | U/O | CDI Social Data Input/Output           | Reserved for   |

| 11  | SPI_SDA | I/O | SPI Serial Data Input/Output           | Register Setup |

| 12  | VSS     | -   | Ground                                 |                |

| 13  | CDI CCI |     | SPI Clock                              | Reserved for   |

| 15  | SPI_SCL | -   | SFI Clock                              | Register Setup |

| 14  | SD      | Ι   | Auto power on/of sequence enable input |                |

| 15  | RST     | Ι   | RESET(L: Reset, H: Active)             |                |

| 16  |         | Ι   | BLUE data Bit B0(LSB)/ LCM ID Pin 1    |                |

| 16  | B0/ID1  | 1   | (Pull-down 10K to VSS by Resistor)     |                |

| 17  | B1      | Ι   | BLUE data Bit B1                       |                |

| 18  | B2      | Ι   | BLUE data Bit B2                       |                |

| 19  | B3      | Ι   | BLUE data Bit B3                       |                |

| 20  | B4      | Ι   | BLUE data Bit B4                       |                |

| 21  | B5      | Ι   | BLUE data Bit B5(MSB)                  |                |

| 22  | CONDO   | т   | GREEN data Bit G0(LSB)/ LCM ID Pin 2   |                |

| 22  | G0/ID2  | Ι   | (Pull-high 10K to DVDD by Resistor)    |                |

| 23  | G1      | Ι   | GREEN data Bit G1                      |                |

| 24  | G2      | Ι   | GREEN data Bit G2                      |                |

| 25  | G3      | Ι   | GREEN data Bit G3                      |                |

| 26  | G4      | Ι   | GREEN data Bit G4                      |                |

| 27  | G5      | Ι   | GREEN data Bit G5(MSB)                 |                |

$\oslash$

|    |        | F |                                                                          |  |

|----|--------|---|--------------------------------------------------------------------------|--|

| 28 | R0/ID0 | Ι | RED data Bit R0(LSB)/ LCM ID Pin 0<br>(Pull-down 10K to VSS by Resistor) |  |

| 29 | R1     | Ι | RED data Bit R1                                                          |  |

| 30 | R2     | Ι | RED data Bit R2                                                          |  |

| 31 | R3     | Ι | RED data Bit R3                                                          |  |

| 32 | R4     | Ι | RED data Bit R4                                                          |  |

| 33 | R5     | Ι | RED data Bit R5(MSB)                                                     |  |

| 34 | VSS    | - | Ground                                                                   |  |

| 35 | DCK    | Ι | Data Sampling Clock Signal                                               |  |

| 36 | VSS    | - | Ground                                                                   |  |

| 37 | VSYNC  | Ι | Vertical sync signal                                                     |  |

| 38 | HSYNC  | Ι | Horizontal sync signal                                                   |  |

| 39 | DENB   | Ι | Data Enable                                                              |  |

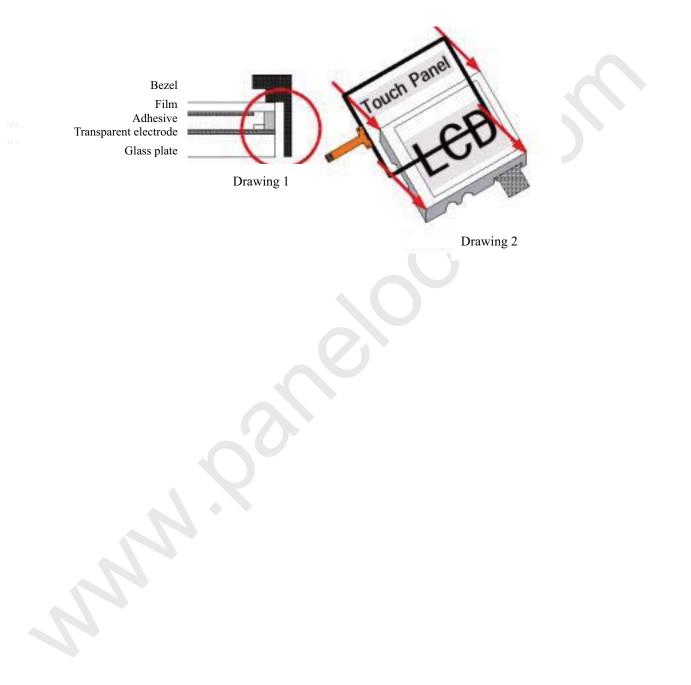

#### 3.2 Touch panel Pin

| Touch Panel Pin | Module Pin | Symbol | Description            | Remark |

|-----------------|------------|--------|------------------------|--------|

| 1               | 9          | XR     | Touch Panel Right Side |        |

| 2               | 8          | YL     | Touch Panel Lower Side |        |

| 3               | 7          | XL     | Touch Panel Left Side  |        |

| 4               | 6          | YU     | Touch Panel Upper Side |        |

Pin Assignment for Touch panel

$\langle p \rangle$

#### 4. ABSOLUTE MAXIMUM RATINGS

|                                            |                  |      |      |      | GND=0V |

|--------------------------------------------|------------------|------|------|------|--------|

| Item                                       | Symbol           | MIN  | MAX  | Unit | Remark |

| Logic Supply Voltage                       | DVDD             | -0.3 | 3.6  | V    |        |

| Analog Supply Voltage                      | AVDD             | -0.3 | 3.6  | V    |        |

| Touch Panel Operation Voltage              | VTouch           | -    | 5    | V    |        |

| Backlight LED forward Voltage              | $V_{\mathrm{F}}$ | -    | 14.4 | V    |        |

| Backlight LED reverse Voltage              | Vr               | -    | 20   | V    |        |

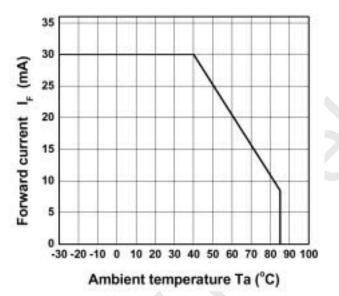

| Backlight LED forward current<br>(Ta=25°C) | I <sub>F</sub>   | -    | 25   | mA   | Note   |

| Operating Temperature                      | Topr             | -20  | +60  | °C   |        |

| Storage Temperature                        | Tstg             | -30  | +70  | °C   |        |

Note: Relation between maximum LED forward current and ambient temperature is showed as bellow.

The information contained herein is the exclusive property of toppoly Optoelectronics corporation, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of toppoly Optoelectronics corporation.

$\langle p \rangle$

#### **5.ELECTRICAL CHARACTERISTICS**

#### 5.1 Driving TET I CD Panel

| 5.1 Driving TFT LCD          | Ta=25°C |                  |         |     |          |        |                         |

|------------------------------|---------|------------------|---------|-----|----------|--------|-------------------------|

| Item                         | Symbol  | MIN              | TYP     | MAX | Unit     | Remark |                         |

| Logic Supply Voltage         |         | DVDD             | 1.6     | 2.8 | 3.3      | V      |                         |

| Logic Supply Voltage Rig     | pple    | —                | —       | —   | 100      | mV     |                         |

| Analog Supply Voltage        |         | AVDD             | 2.5     | 2.8 | 3.3      | V      |                         |

| Analog Supply Voltage Ripple |         | —                | —       | —   | 100      | mV     |                         |

| Lagia Input Valtaga          | High    | VIH              | 0.8DVDD | _   | DVDD+0.3 | V      | DCK,HSYNC,              |

| Logic Input Voltage          | Low     | VIL              | VSS-0.3 | _   | 0.2DVDD  | V      | VSYNC,DENB<br>,DATA,SPI |

| Leakage current              |         | IL               | -1      | _   | 1        | uA     |                         |

| DVDD/AVDD Supply (           | Current | I <sub>VDD</sub> | -       | 6.0 | 6.4      | mA     |                         |

Note 1: Power consumption test condition

a. Input voltage: 2.8V

b. Test pattern:

#### 5.2 Driving backlight

|        | -°~ |

|--------|-----|

| 1.2=7- | )(. |

| Item                    | Symbol           | MIN | TYP   | MAX | Unit | Remark             |

|-------------------------|------------------|-----|-------|-----|------|--------------------|

| Forward Current         | $I_{\mathrm{F}}$ | -   | 20    | 25  | mA   | LED/Part           |

| LED Life Time           | -                | -   | 10000 | -   | Hr   | IF: 20mA           |

| Forward Current Voltage | $V_{\text{F}}$   | -   | 14.4  | 16  | V    | IF: 20mA ,LED/Part |

Note: Backtlight driving circuit is recommend as the fix current circuit.

$\langle p \rangle$

5.3 Driving touch panel (Analog resistance type)

Ta=25°C

|                                    | 1a-23 C            |      |     |      |      |            |

|------------------------------------|--------------------|------|-----|------|------|------------|

| Item                               | Symbol             | MIN  | TYP | MAX  | Unit | Remark     |

| Resistor between terminals (XR-XL) | Rx                 | 200  | -   | 1300 | Ω    |            |

| Resistor between terminals (YU-YL) | Ry                 | 200  | -   | 1300 | Ω    |            |

| Operation Voltage                  | $V_{\text{Touch}}$ | -    | 5   | -    | V    | DC         |

| Line Linearity (X direction)       | -                  | -1.5 | -   | +1.5 | %    | Note       |

| Line Linearity (Y direction)       | -                  | -1.5 | -   | +1.5 | %    | Note       |

| Chattering                         | -                  | -    | 10  | -    | ms   |            |

| Surface Hardness                   | -                  | 3    | -   | -    | Н    | JIS K 5600 |

| Minimum tension for detecting      | -                  | -    | -   | 80   | g    |            |

| Insulation Resistance              | Ri                 | 20   | -   | -    | MΩ   | At DC 25V  |

Note. The minimum test force is 80 g.

The information contained herein is the exclusive property of toppoly Optoelectronics corporation, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of toppoly Optoelectronics corporation.

$\langle p \rangle$

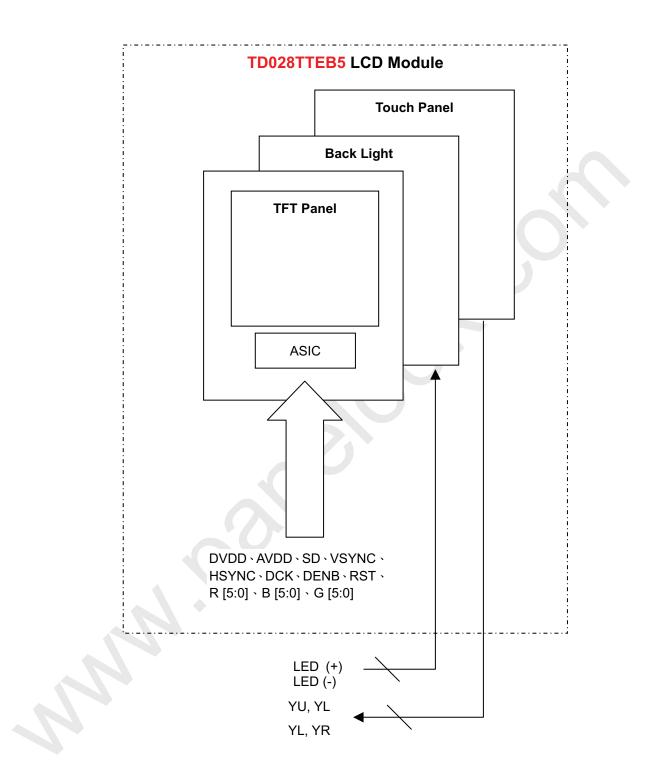

#### 6. BLOCK DIAGRAM

$\langle p \rangle$

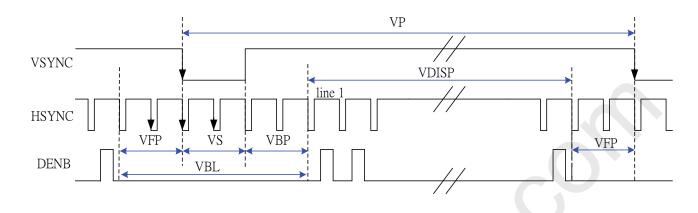

#### 7. TIMING CHART

7.1 Display timing

| Display | Davamatar                  | Symbol | Conditions |     | Rating | S   | IIn:4 | Domoniz |

|---------|----------------------------|--------|------------|-----|--------|-----|-------|---------|

| Mode    | Parameter                  | Symbol | Conditions | MIN | TYP    | MAX | Unit  | Remark  |

|         | Vertical Cycle             | VP     |            | 430 | 435    | 450 | Line  |         |

|         | Vertical Pulse Low width   | VS     |            | 1   | 2      | _   |       |         |

|         | Vertical Data Start        | VDS    | VS+VBP     | 2   | 4      | 15  | Line  | *Note1  |

|         | Vertical Front Porch       | VFP    |            | 108 | 111    | _   | Line  |         |

|         | Vertical Blanking Period   | VBL    | VS+VBP+VFP | 110 | 115    | _   | Line  |         |

|         | Vertical Active Area       | VDISP  |            | _   | 320    | -   | Line  |         |

| Normal  | Horizontal Cycle           | HP     |            | 260 | 280    | 300 | dot   |         |

| rtormar | Horizontal Pulse Low Width | HS     |            | 2   | 10     | -   | dot   |         |

|         | Horizontal Data Start      | HDS    | HS+HBP     | 10  | 30     | 63  | dot   | *Note2  |

|         | Horizontal Front Porch     | HFP    |            | —   | 10     |     | dot   |         |

|         | Horizontal Blanking Period | HBL    | VS+VBP+VFP | 20  | 40     | -   |       |         |

|         | Horizontal Active Area     | HDISP  |            | _   | 240    | -   | dot   |         |

|         | Clock Frequency            | fDCK   |            | 6.7 | 7.3    | 8.5 | MHz   |         |

|         | Clock Flequency            | tDCK   |            | 149 | 136    | 118 | nS    |         |

Note1 Please change the register R3 via SPI command to modify the VDS(Min./Max.)

Note2 Please change the register R4 via SPI command to modify the HDS(Min./Max.)

The information contained herein is the exclusive property of toppoly Optoelectronics corporation, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of toppoly Optoelectronics corporation.

$\langle p \rangle$

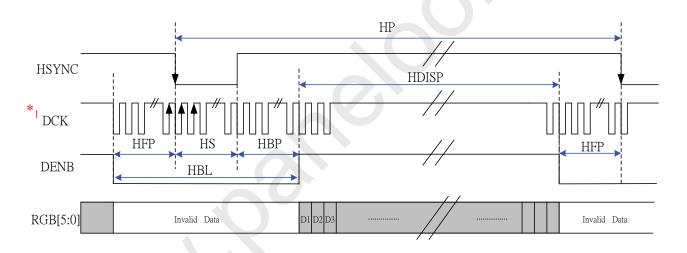

- 7.2 Input timing chart

- <Vertical Timing chart>

<Horizontal Timing chart>

\*1 The frequency of DCK should be continued whether in display or blank region to ensure IC operating normally.

Note:

(1) In VS+HS mode , just remove the DE signal , all the other timing is the same • Please change the register R2 via SPI command to modify the VS+HS mode •

The information contained herein is the exclusive property of toppoly Optoelectronics corporation, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of toppoly Optoelectronics corporation.

$\oslash$

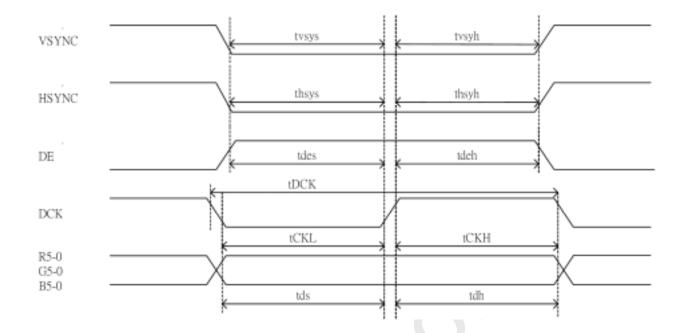

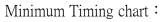

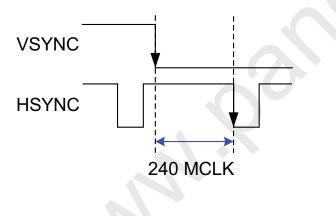

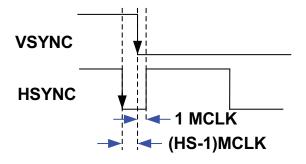

#### 7.3 Setup / Hold Timing chart

Phase difference of Sync.(thv) : Maximum Timing chart :

The information contained herein is the exclusive property of toppoly Optoelectronics corporation, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of toppoly Optoelectronics corporation.

$\oslash$

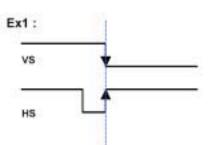

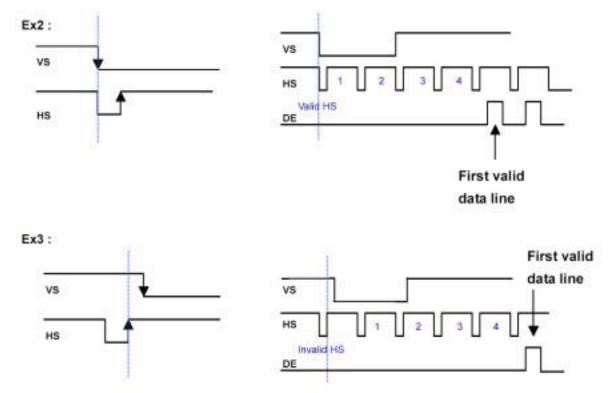

If the VS falling edge and HS rising edge are in the same time, the timing is in the margin and not surely which is the first valid data line.

If VS falling edge is delay some time after HS rising edge, this timing will cause the first valid data line delay one HS time.

The information contained herein is the exclusive property of toppoly Optoelectronics corporation, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of toppoly Optoelectronics corporation.

$\oslash$

| Parameter                                        | Symbol | Conditions |         | Ratings | atings |      |  |

|--------------------------------------------------|--------|------------|---------|---------|--------|------|--|

| Parameter                                        | Symbol | Conditions | MIN     | TYP     | MAX    | Unit |  |

| Vertical Sync. Setup time                        | tvsys  |            | 20      | _       | —      | ns   |  |

| Vertical Sync. Hold time                         | tvsyh  |            | 20      | _       | —      | ns   |  |

| Horizontal Sync. Setup time                      | thsys  |            | 20      | —       | —      | ns   |  |

| Horizontal Sync. Hold time                       | thsyh  |            | 20      | —       | _      | ns   |  |

| Phase difference of Sync.<br>Signal Falling edge | thv    |            | -(HS-1) | _       | 240    | DCK  |  |

| Clock Low Priod                                  | tCKL   |            | 75      | -       |        | ns   |  |

| Clock High Priod                                 | tCKH   |            | 75      |         |        | ns   |  |

| Data setup time                                  | tds    |            | 20      |         | -      | ns   |  |

| Data Hold time                                   | tdh    |            | 20      | _       | _      | ns   |  |

| DE setup time                                    | tdes   |            | 30      |         | —      | ns   |  |

| DE Hold time                                     | tdeh   |            | 30      | -       | _      | ns   |  |

Note: Thy range if it can't meet our spec, just give up first Hsync. It can't impact any side effect.

The information contained herein is the exclusive property of toppoly Optoelectronics corporation, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of toppoly Optoelectronics corporation.

#### <SERIAL INTERFACE>

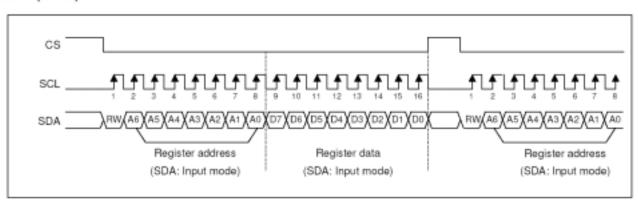

The LCM support the 3-pin serial interface to set internal register. Read/Write bit RW, Serial address A6 to A0 and serial data D7 to D0 are read at the rising edge of the serial clock, via the serial input pin. This data is synchronized on the rising edge of eighth serial clock and is then converted to parallel data. The serial interface signal timing chart is shown below.

#### Serial interface signal timing chart

#### Write Mode (RW=L)

The shift register and counter are reset to their initial values when the chip select signal is inactive. Do not set the chip select signal to inactive between transmission of an 8-bit address and 8-bit data set for the command.

When using SCL wiring, the module has to be designed carefully to avoid any noise coming from reflection or from external sources. We recommand checking operation with the actual module.

If there is a break in data transmission by RESETB or CS pulse, while transferring a Command or Parameter, before Bit D0 of the byte has been completed, then LCM will reject the previous bits and have reset the interface such that it will be ready to receive the same byte re-transmitted when the chip select line (CS) is activated after RESETB have been High state.

The information contained herein is the exclusive property of toppoly Optoelectronics corporation, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of toppoly Optoelectronics corporation.

$\langle p \rangle$

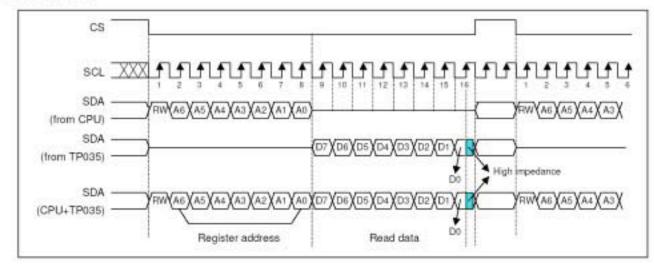

#### Read Mode (RW=H)

The read mode of the interface means that the micro controller reads data from the LCM. To do so the micro controller first has to send a command: the read status command. Then the following byte is transmitted in the opposite direction. After that CS is required to go high.

The LCM samples the SDA data input at rising SCL edges, but shifts SDA data output at falling SCL edges. Thus the micro controller is supposed to read SDA data at rising SCL edges.

After the read status command has been sent, the SDA line must be set to tristate not later then at the rising SCL edge of the last bit.

The LCM can read data of the Register0 to Register63

The information contained herein is the exclusive property of toppoly Optoelectronics corporation, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of toppoly Optoelectronics corporation.

tpo

### TD028TTEB5

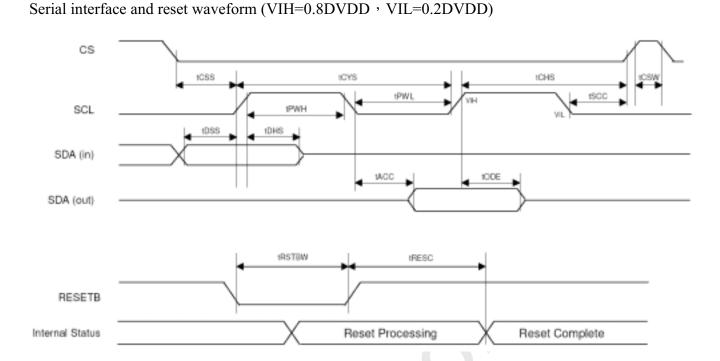

| Serial interface and Reset | Serial interface and Reset |            |      |      |      |      |  |  |  |  |

|----------------------------|----------------------------|------------|------|------|------|------|--|--|--|--|

| Parameter                  | Symbol                     | Conditions | Min. | Тур. | Max. | Unit |  |  |  |  |

| Clock cycle                | tCYS                       | -          | 150  | -    | -    | ns   |  |  |  |  |

| Clock High Period          | tPWH                       |            | 60   | -    | -    | ns   |  |  |  |  |

| Clock Low Period           | tPWL                       | -          | 60   | -    | -    | ns   |  |  |  |  |

| Data Set-up Time           | tDSS                       | -          | 60   | -    | -    | ns   |  |  |  |  |

| Data Hold Time             | tDHS                       | -          | 60   | -    | -    | ns   |  |  |  |  |

| CS High width              | tCSW                       | -          | 1    | -    | -    | us   |  |  |  |  |

| CS Set-up Time             | tCSS                       | -          | 60   | -    | -    | ns   |  |  |  |  |

| CS Hold Time               | tCHS                       | -          | 70   | -    | -    | ns   |  |  |  |  |

| SCL to CS                  | tSCC                       |            | 40   | -    | -    | ns   |  |  |  |  |

| Output Access Time         | tACC                       |            | 10   | -    | 50   | ns   |  |  |  |  |

| Output Disable Time        | tODE                       |            | 25   | -    | 80   | ns   |  |  |  |  |

| RSTB low width             | tRSTBW                     | -          | 1000 | -    | -    | ns   |  |  |  |  |

| RESET complete time        | tRESC                      | -          | -    | -    | 1000 | ns   |  |  |  |  |

tpo

#### **Command descriptions :**

Reset the internal register by setting low level the RESET pin or software reset command.

| Register | Default |              |     |          | S        | Setting      | g valu    | ıe       |          |          |                                                                      |                                   |  |  |  |

|----------|---------|--------------|-----|----------|----------|--------------|-----------|----------|----------|----------|----------------------------------------------------------------------|-----------------------------------|--|--|--|

| [Dec]    | [Hex]   | Bit name     | D7  | D6       | 1        | D4           |           | D2       | D1       | D0       | Description                                                          | Remark                            |  |  |  |

|          | 85h     | CHIPID[2:0]  |     |          |          |              |           |          |          |          | Chip ID (Read only)                                                  | The Chip ID can be changed by     |  |  |  |

| R0       | 001     | 0111112[2:0] | 1   |          |          |              |           |          |          |          | D7=1 for SPFD5413C                                                   | MASK Option.                      |  |  |  |

|          |         |              | -   |          | 0        | 0            | 0         |          |          |          | ID 0                                                                 |                                   |  |  |  |

|          |         |              |     |          | 0        | 0            | 1         |          |          |          | ID 1                                                                 |                                   |  |  |  |

|          |         |              |     |          | -        | -            | -         |          |          |          | -                                                                    |                                   |  |  |  |

|          |         |              |     |          | 1        | 1            | 1         |          |          |          | ID 7                                                                 |                                   |  |  |  |

|          |         | REVID[2:0]   |     |          |          |              |           |          |          |          | Revision ID (Read only)                                              | The Revision ID can be changed by |  |  |  |

|          |         |              |     |          |          |              |           | 0        | 0        | 0        | REV 0                                                                | MASK Option.                      |  |  |  |

|          |         |              |     |          |          |              |           | 0        | 0        | 1        | REV 1                                                                |                                   |  |  |  |

|          |         |              |     |          |          |              |           | 0        | 1        | 0        | REV 2                                                                |                                   |  |  |  |

|          |         |              |     |          |          |              |           | 0        | 1        | 1        | REV 3                                                                |                                   |  |  |  |

|          |         |              |     |          |          |              |           | 1        | 0        | 0        | REV 4                                                                |                                   |  |  |  |

|          |         |              |     |          |          |              |           | 1        | 0        | 1        | REV 5                                                                |                                   |  |  |  |

|          |         |              |     |          |          |              |           | 1        | 1        | 0        | REV 6                                                                |                                   |  |  |  |

|          |         |              |     |          |          |              |           | 1        | 1        | 1        | REV 7                                                                |                                   |  |  |  |

| R1       | 00h     | VCM[7:5]     |     |          |          |              |           |          |          |          | VCOM amplitude adjustment by VCOMH voltage change at full color mode | VCOMH voltage change at full col- |  |  |  |

|          |         |              | 0   | 1        | 1        |              |           |          |          |          | 150 mV                                                               | mode                              |  |  |  |

|          |         |              | 0   | 1        | 0        |              |           |          |          |          | 100 mV                                                               |                                   |  |  |  |

|          |         |              | 0   | 0        | 1        |              |           |          |          |          | 50 mV                                                                |                                   |  |  |  |

|          |         |              | 0   | 0        | 0        |              |           |          |          |          | 0 mV                                                                 |                                   |  |  |  |

|          |         |              | 1   | 0        | 0        |              |           |          |          |          | -50 mV                                                               |                                   |  |  |  |

|          |         |              | 1   | 0        | 1        |              |           |          |          |          | -100 mV                                                              |                                   |  |  |  |

|          |         |              | 1   | 1        | 0        |              |           |          |          |          | -150 mV                                                              |                                   |  |  |  |

|          |         |              | 1   | 1        | 1        |              |           |          |          |          | -200 mV                                                              |                                   |  |  |  |

|          |         | VCM[4:0]     |     |          |          |              |           |          |          |          | VCOM voltage select at full color mode                               | VCOM_DC value setting at full     |  |  |  |

|          |         |              |     |          |          | 0            | 1         | 1        | 1        | 1        | VCOMH=4.305V, VCOML=0.705V                                           | color mode                        |  |  |  |

|          |         |              |     |          |          | 0            | 1         | 1        | 1        | 0        | VCOMH=4.290V, VCOML=0.690V                                           |                                   |  |  |  |

|          |         |              |     |          |          | 0            | 1         | 1        | 0        | 1        | VCOMH=4.275V, VCOML=0.675V                                           |                                   |  |  |  |

|          |         |              |     |          |          | 0            | 1         | 1        | 0        | 0        | VCOMH=4.260V, VCOML=0.660V                                           |                                   |  |  |  |

|          |         |              |     |          |          | 0            | -         | -        | -        | -        | -                                                                    |                                   |  |  |  |

|          |         |              |     |          |          | 0            | 0         | 0        | 0        | 1        | VCOMH=4.095V,VCOML=0.495V                                            | _                                 |  |  |  |

|          |         |              |     |          |          | 0            | 0         | 0        | 0        | 0        | VCOMH=4.080V,VCOML=0.480V                                            |                                   |  |  |  |

|          |         |              |     |          |          | 1            | 0         | 0        | 0        | 0        | VCOMH=4.065V,VCOML=0.465V                                            |                                   |  |  |  |

|          |         |              |     |          |          | 1            | 0         | 0        | 0        | 1        | VCOMH=4.050V,VCOML=0.450V                                            |                                   |  |  |  |

|          |         |              |     |          |          | 1            | -         | -        | -        | -        |                                                                      |                                   |  |  |  |

|          |         |              |     | -        | -        | 1            | 1         | 1        | 0        | 1        | VCOMH=3.870V,VCOML=0.270V                                            |                                   |  |  |  |

|          |         |              |     |          |          | -            | 1         | 1        | 1        | 0        | VCOMH=3.855V,VCOML=0.255V                                            |                                   |  |  |  |

|          |         |              |     |          |          | 1            | 1         | 1        | 1        | 1        | VCOMH=3.840V,VCOML=0.240V                                            |                                   |  |  |  |

|          |         |              |     |          |          |              |           |          |          |          |                                                                      |                                   |  |  |  |

|          |         |              | ├── | +        | +        | <del> </del> |           |          |          |          |                                                                      |                                   |  |  |  |

| D2       | 0.01    | GVALCE       | —   |          |          |              | $\square$ |          |          | ┢        |                                                                      | Medealastica                      |  |  |  |

| R2       | 00h     | SYNCP        | ├   | 0        |          |              |           |          |          | -        | SYNC polarity select                                                 | Mode slection                     |  |  |  |

|          |         |              |     | 0        |          |              |           |          |          |          | Negative                                                             | _                                 |  |  |  |

|          |         |              |     | 1        |          |              |           |          |          |          | Positive                                                             |                                   |  |  |  |

|          |         | DINT         | _   | <u> </u> |          |              |           | <u> </u> | <u> </u> | <u> </u> | Input data mapping select                                            |                                   |  |  |  |

|          |         |              |     | <b> </b> | 0        |              |           | <u> </u> | L        |          | 18 bit interface (262k color)                                        |                                   |  |  |  |

|          |         |              |     | -        | 1        | I            |           |          | <u> </u> | -        | 16 bit interface (65k color, R:G:B=5:6:5)                            | <b>—</b>                          |  |  |  |

|          |         | DCKP         |     | <u> </u> | _        |              | -         |          | <u> </u> | -        | Input clock polarity change                                          | _                                 |  |  |  |

|          |         |              |     |          |          | 0            | <u> </u>  |          | <u> </u> |          | No change                                                            |                                   |  |  |  |

|          |         |              | _   | _        | _        | 1            | -         |          | <u> </u> | -        | Change                                                               |                                   |  |  |  |

|          |         | MSEL         |     | <u> </u> | <u> </u> | <u> </u>     |           |          |          |          | Input Timing Model Select                                            | _                                 |  |  |  |

|          |         |              | ┣── |          |          |              | <u> </u>  |          | 0        | 0        | HS+VS+DE                                                             | _                                 |  |  |  |

|          |         |              | L   | <b> </b> | <b> </b> | I            |           | L        | 0        | 1        | HS+VS                                                                |                                   |  |  |  |

|          |         |              | 1   |          |          |              |           | <u> </u> | - 1      | -        | -                                                                    |                                   |  |  |  |

.

### TD028TTEB5

$\oslash$

| Register | Default |           |    |          | S | Setting value |   |        |    |    |                                                                       |                                     |  |  |

|----------|---------|-----------|----|----------|---|---------------|---|--------|----|----|-----------------------------------------------------------------------|-------------------------------------|--|--|

| [Dec]    | [Hex]   | Bit name  | D7 | D6       |   | <u> </u>      |   |        | D1 | D0 | Description                                                           | Remark                              |  |  |

| R3       | 04h     | VSTS[3:0] |    | l        | l |               |   |        |    |    | Vertical valid data start time select (VDS)                           |                                     |  |  |

|          |         |           |    |          |   |               | 0 | 0      | 0  | 0  | 2 HSYNC                                                               | 1                                   |  |  |

|          |         |           |    |          |   |               | 0 | 0      | 0  | 1  | 2 HSYNC                                                               |                                     |  |  |

|          |         |           |    |          |   |               | 0 | 0      | 1  | 0  | 2 HSYNC                                                               |                                     |  |  |

|          |         |           |    |          |   |               | 0 | 0      | 1  | 1  | 3 HSYNC                                                               |                                     |  |  |

|          |         |           |    |          |   |               | 0 | 1      | 0  | 0  | 4 HSYNC                                                               |                                     |  |  |

|          |         |           |    |          |   |               | 0 | 1      | 0  | 1  | 5 HSYNC                                                               |                                     |  |  |

|          |         |           |    |          |   |               | - | -      | -  | -  | -                                                                     |                                     |  |  |

|          |         |           |    |          |   |               | 1 | 1      | 1  | 1  | 15 HSYNC                                                              |                                     |  |  |

| R4       | 1Eh     | HSTS[5:0] |    |          |   |               |   |        |    |    | Horizontal valid data start time select (HDS)                         |                                     |  |  |

|          |         |           |    |          | 0 | 0             | 0 | 0      | 0  | 0  | 10 DCK                                                                |                                     |  |  |

|          |         |           |    |          | 0 | 0             | 0 | 0      | 0  | 1  | 10 DCK                                                                |                                     |  |  |

|          |         |           |    |          | 0 | 0             | 0 | 0      | 1  | 0  | 10 DCK                                                                |                                     |  |  |

|          |         |           |    |          | 0 | 0             | 0 | 0      | 1  | 1  | 10 DCK                                                                |                                     |  |  |

|          |         |           | -  |          | 0 | 0             | 0 | 1      | 0  | 0  |                                                                       |                                     |  |  |

|          |         |           |    |          | 0 | 0             | 0 | 1      | 0  | 1  | 10 DCK                                                                |                                     |  |  |

|          |         |           |    |          | 0 | 0             | 0 | 1      | 1  | 0  | 10 DCK                                                                | · ·                                 |  |  |

|          |         |           |    |          | 0 | 0             | 0 | 1      | 1  | 1  | 10 DCK                                                                |                                     |  |  |

|          |         |           |    |          | 0 | 0             | 1 | 0      | 0  | 0  | 10 DCK<br>10 DCK                                                      |                                     |  |  |

|          |         |           | -  |          | 0 | 0             | 1 | 0      | 1  | 0  | 10 DCK                                                                |                                     |  |  |

|          |         |           |    |          | 0 | 0             | 1 | 0      | 1  | 1  | 11 DCK                                                                |                                     |  |  |

|          |         |           |    |          | 0 | 0             | 1 | 1      | 0  | 0  | 12 DCK                                                                |                                     |  |  |

|          |         |           |    |          | - | -             | - | -      | -  | -  | -                                                                     |                                     |  |  |

|          |         |           |    |          | 0 | 1             | 1 | 1      | 1  | 0  | 30 DCK                                                                |                                     |  |  |

|          |         |           |    |          | - | -             | - | -      | -  | -  |                                                                       |                                     |  |  |

|          |         |           |    |          | 1 | 1             | 1 | 1      | 1  | 1  | 63 DCK                                                                |                                     |  |  |

| R5       | 01h     | PARS[7:0] |    |          |   |               |   |        |    |    | Partial start line select                                             | When VSYNC+HSYNC+DE mode,           |  |  |

|          |         |           | 0  | 0        | 0 | 0             | 0 | 0      | 0  | 0  | Do not setting when PARS[8]=0, Gate256 is selected when PARS[8]=1     | DE=H: Normal display line           |  |  |

|          |         |           | 0  | 0        | 0 | 0             | 0 | 0      | 0  | 1  | Gate1 is selected when PARS[8]=0, Gate257 is selected when PARS[8]=1  | DE=L: Non-display line (White)      |  |  |

|          |         |           | 0  | 0        | 0 | 0             | 0 | 0      | 1  | 0  | Gate2 is selected when PARS[8]=0, Gate258 is selected when PARS[8]=1  |                                     |  |  |

|          |         |           | 0  | 0        | 0 | 0             | 0 | 0      | 1  | 1  | Gate3 is selected when PARS[8]=0, Gate259 is selected when PARS[8]=1  | When VSYNC+HSYNC mode,              |  |  |

|          |         |           | -  | -        | - | -             | - | -      | -  | -  | -                                                                     | Normal display line can be selected |  |  |

|          |         |           | 0  | 0        | 1 | 1             | 1 | 1      | 1  | 1  | Gate63 is selected when PARS[8]=0, Gate319 is selected when PARS[8]=1 | by R5,6,7 and 8.                    |  |  |

|          |         |           | 0  | 1        | 0 | 0             | 0 | 0      | 0  | 0  | Gate64 is selected when PARS[8]=0, Gate320 is selected when PARS[8]=1 |                                     |  |  |

|          |         |           | 0  | 1        | 0 | 0             | 0 | 0      | 0  | 1  | Gate65 is selected when PARS[8]=0, Do not setting when PARS[8]=1      |                                     |  |  |

|          |         |           | 0  | 1        | 0 | 0             | 0 | 0      | 1  | 0  | Gate66 is selected when PARS[8]=0, Do not setting when PARS[8]=1      |                                     |  |  |

|          |         |           | -  | -        | - | -             | - | -      | -  | -  |                                                                       |                                     |  |  |

|          |         |           | 1  | 1        | 1 | 1             | 1 | 1      | 0  | 0  | Gate252 is selected when PARS[8]=0, Do not setting when PARS[8]=1     |                                     |  |  |

|          |         |           | 1  | 1        | 1 | 1             | 1 | 1      | 0  | 1  | Gate253 is selected when PARS[8]=0, Do not setting when PARS[8]=1     |                                     |  |  |

|          |         |           | 1  | 1        | 1 | 1             | 1 | 1      | 1  | 0  | Gate254 is selected when PARS[8]=0, Do not setting when PARS[8]=1     |                                     |  |  |

|          |         |           | 1  | 1        | 1 | 1             | T | 1      | 1  | 1  | Gate255 is selected when PARS[8]=0, Do not setting when PARS[8]=1     | ł                                   |  |  |

| R6       | 00h     | PARS[8]   | L  | I        | I |               |   |        |    |    | Partial start line select                                             |                                     |  |  |

|          |         |           |    | <u> </u> |   |               | _ |        |    | 0  | Gate1 – Gate255 is selected                                           |                                     |  |  |

|          |         |           | 1  |          |   |               |   | $\sim$ |    | 1  | Gate256 – Gate320 is selected                                         |                                     |  |  |

$\oslash$

| Register | Default                       | Bit name   | Setting value |          |     |    |     |        |    | Description | Remark                                                                |                                                               |  |  |  |  |

|----------|-------------------------------|------------|---------------|----------|-----|----|-----|--------|----|-------------|-----------------------------------------------------------------------|---------------------------------------------------------------|--|--|--|--|

| [Dec]    | [Hex]                         | Dir Hame   | D7            | D6       | D5  | D4 | D3  | D2     | D1 | D0          | Description                                                           | ACHIAI K                                                      |  |  |  |  |

| R7       | 20h                           | PARE[7:0]  |               |          |     |    |     |        |    |             | Partial end line select                                               | When VSYNC+HSYNC+DE mod                                       |  |  |  |  |

|          |                               |            | 0             | -        | 0   |    | 0   | 0      | 0  | 0           |                                                                       | DE=H: Normal display line                                     |  |  |  |  |

|          |                               |            | 0             | 0        | 0   | 0  | 0   | 0      | 0  | 1           | Gate1 is selected when PARE[8]=0, Gate257 is selected when PARE[8]=1  | DE=L: Non-display line (White)                                |  |  |  |  |

|          |                               |            | 0             | 0        | 0   | 0  | 0   | 0      | 1  | 0           | Gate2 is selected when PARE[8]=0, Gate258 is selected when PARE[8]=1  | When VSVNC USVNC mode                                         |  |  |  |  |

|          |                               |            | 0             | 0        | 0   | 0  | 0   | 0      | 1  | 1           | Gate3 is selected when PARE[8]=0, Gate259 is selected when PARE[8]=1  | When VSYNC+HSYNC mode,<br>Normal display line can be selected |  |  |  |  |

|          |                               |            | -             | -        | -   | -  | -   | -      | -  | -           |                                                                       | by R5,6,7 and 8.                                              |  |  |  |  |

|          |                               |            | 0             | 0        | 0   | 1  | 1   | 1      | 1  | 1           | Gate31 is selected when PARE[8]=0, Gate286 is selected when PARE[8]=1 |                                                               |  |  |  |  |

|          |                               |            | 0             | 0        | 1   | 0  | 0   | 0      | 0  | 0           | Gate32 is selected when PARE[8]=0, Gate287 is selected when PARE[8]=1 | -                                                             |  |  |  |  |

|          |                               |            | 0             | 0        | 1   | 0  | 0   | 0      | 0  | 1           | Gate33 is selected when PARE[8]=0, Gate288 is selected when PARE[8]=1 | _                                                             |  |  |  |  |

|          |                               |            | 0             | 0        | -   | -  | -   | 0      | 1  | 0           | Gate34 is selected when PARE[8]=0, Gate289 is selected when PARE[8]=1 | -                                                             |  |  |  |  |

|          |                               |            | 0             | 0        | - 1 | -  | - 1 | - 1    | -  | - 1         | Gate63 is selected when PARE[8]=0, Gate319 is selected when PARE[8]=1 | -                                                             |  |  |  |  |

|          |                               |            | 0             | 1        | 0   | 0  | 0   | 0      | 0  | 0           | Gate64 is selected when PARE[8]=0, Gate319 is selected when PARE[8]=1 |                                                               |  |  |  |  |

|          |                               |            | 0             | 1        | 0   | 0  | 0   | 0      | 0  | 1           | Gate65 is selected when PARE[8]=0, Do not setting when PARE[8]=1      | -                                                             |  |  |  |  |

|          |                               |            | 0             | 1        | 0   | 0  | 0   | 0      | 1  | 0           | Gate66 is selected when PARE[8]=0, Do not setting when PARE[8]=1      |                                                               |  |  |  |  |

|          |                               |            | 0             | -        | -   | -  | -   | -      | 1  | 0           | Gateoo is selected when FARE[o]=0, Do not setting when FARE[o]=1      | -                                                             |  |  |  |  |

|          |                               |            | 1             | 1        | 1   | 1  | 1   | 1      | 0  | 0           | Gate252 is selected when PARE[8]=0, Do not setting when PARE[8]=1     |                                                               |  |  |  |  |

|          |                               |            | 1             | 1        | 1   | 1  | 1   | 1      | 0  | 1           | Gate252 is selected when PARE[8]=0, Do not setting when PARE[8]=1     | -                                                             |  |  |  |  |

|          |                               |            | 1             | 1        | 1   | 1  | 1   | 1      | 1  | 0           | Gate255 is selected when PARE[8]=0, Do not setting when PARE[8]=1     | 4                                                             |  |  |  |  |

|          |                               |            | 1             | 1        | 1   | 1  | 1   | 1      | 1  | 1           | Gate255 is selected when PARE[8]=0, Do not setting when PARE[8]=1     | -                                                             |  |  |  |  |

| R8       | 00h                           | PARE[8]    |               | <u> </u> | -   | -  |     | -      |    | -           | Partial end line select                                               | 4                                                             |  |  |  |  |

| 100      | 0 Gate1 – Gate255 is selected |            | -             |          |     |    |     |        |    |             |                                                                       |                                                               |  |  |  |  |

|          |                               |            | -             | 1        | 1   |    |     |        |    | 1           | Gate256 – Gate320 is selected                                         | -                                                             |  |  |  |  |

| R9       | C1h                           | RL         |               | -        |     |    |     |        |    |             | Shift direction (right / left)                                        |                                                               |  |  |  |  |

| К9       | CIII                          | KL         | 0             | +        | +   |    |     |        |    |             | D240 to D1                                                            |                                                               |  |  |  |  |

|          |                               |            | 1             |          | -   |    |     |        |    |             | D1 t0 D240                                                            |                                                               |  |  |  |  |

|          | TB                            | TB         | 1             |          | -   |    |     |        |    | -           | Shift direction (top / bottom)                                        | -                                                             |  |  |  |  |

|          |                               | 15         | -             | 0        | 1   |    |     |        |    |             | Bottom to top                                                         | -                                                             |  |  |  |  |

|          |                               |            |               | 1        | -   |    |     |        |    |             | Top to bottom                                                         | -                                                             |  |  |  |  |

|          |                               | СМ         |               |          | 1   |    |     |        |    |             | Full color or partial color setup                                     | -                                                             |  |  |  |  |

|          |                               |            |               | 1        | 0   |    |     |        |    |             | Normal (262K color)                                                   |                                                               |  |  |  |  |

|          |                               |            |               | 1        | 1   |    |     |        |    |             | Partial(8 color)                                                      | _                                                             |  |  |  |  |

|          |                               | RESOL[1:0] |               |          |     |    |     |        |    |             | Resolution mode select                                                | -                                                             |  |  |  |  |

|          |                               |            |               | 1        |     | 0  | 0   |        |    |             | 240 x RGB x 320                                                       |                                                               |  |  |  |  |

|          |                               |            |               |          |     | 1  | 1   |        |    |             | 240 x RGB x 240                                                       |                                                               |  |  |  |  |

|          |                               | INVSEL     |               |          |     |    |     |        |    |             | Invert mode eclect                                                    |                                                               |  |  |  |  |

|          |                               |            |               |          |     |    |     | 0      |    |             | Line inversion                                                        |                                                               |  |  |  |  |

|          |                               |            |               |          |     |    |     | 1      |    | $\times$    | Frame inversion                                                       |                                                               |  |  |  |  |

|          |                               | STV1       |               |          |     |    |     |        |    |             | STV1(single / main panel) signal control                              |                                                               |  |  |  |  |

|          |                               |            |               |          |     |    |     |        | 0  |             | STV1 signal output                                                    |                                                               |  |  |  |  |

|          |                               |            |               |          |     |    |     |        | 1  |             | STV1 signal not output                                                | _                                                             |  |  |  |  |

|          |                               | STV2       |               |          | _   |    |     |        |    |             | STV2(dual / sub panel) signal control                                 |                                                               |  |  |  |  |

|          |                               |            | L             | $\vdash$ | _   |    | Ş., |        |    | 0           | STV2 signal output                                                    | _                                                             |  |  |  |  |

|          |                               |            |               | <u> </u> |     |    |     |        |    | 1           | STV2 signal not output                                                |                                                               |  |  |  |  |

| R10      | 00h                           | CMDR       | L             |          |     |    |     | $\sim$ |    |             | Software reset                                                        |                                                               |  |  |  |  |

|          |                               |            |               |          |     |    |     |        |    | 0           | Normal                                                                | _                                                             |  |  |  |  |

|          |                               |            |               |          |     |    |     |        |    |             | Software reset                                                        |                                                               |  |  |  |  |

肩库:全球液晶屏交易中心

### TD028TTEB5

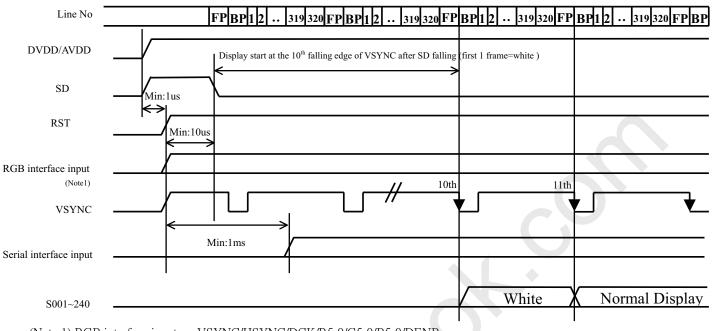

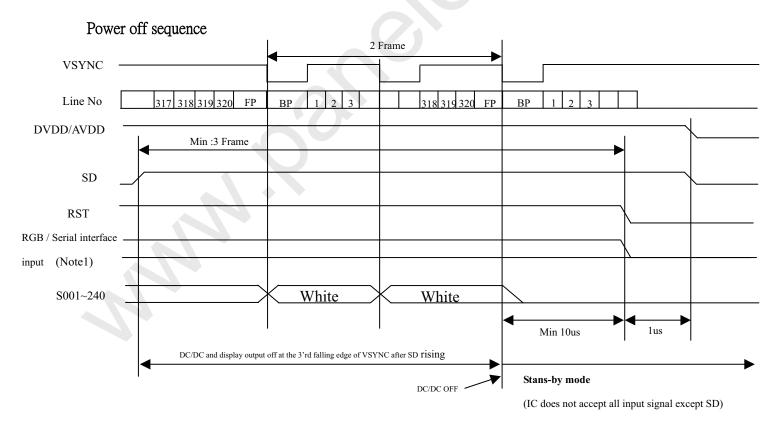

#### 8. Power On/Off Sequence

Power on sequence

(Note 1) RGB interface input - VSYNC/HSYNC/DCK/R5-0/G5-0/B5-0/DENB

(Note 1) RGB interface input - VSYNC/HSYNC/DCK/R5-0/G5-0/B5-0/DENB

The information contained herein is the exclusive property of toppoly Optoelectronics corporation, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of toppoly Optoelectronics corporation.

Page: 22/37

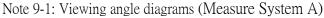

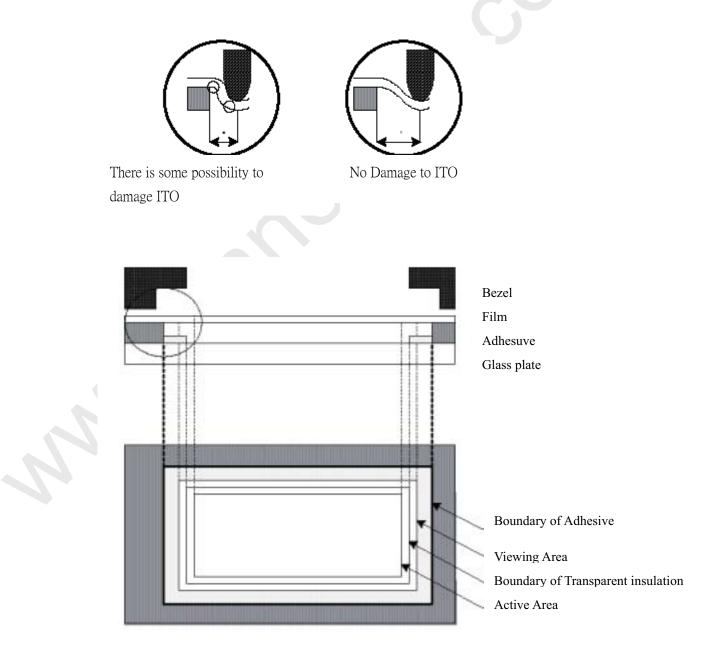

#### 9. Optical Characteristics

9.1 Optical Specification

|                |        |        |                      |       |                                              |                |        | Ta=25°C  |                   |          |

|----------------|--------|--------|----------------------|-------|----------------------------------------------|----------------|--------|----------|-------------------|----------|

| Item           | Symbo  | ol     | Condition            | MIN   | TYP                                          | MAX            | Unit   | Remarks  |                   |          |

|                | θ11(F  | R)     |                      | 45    | 55                                           | -              |        |          |                   |          |

| Viewing Angles | θ12(I  | .)     | CR ≥ 10              | 45    | 55                                           | -              | Degree | Note 9-1 |                   |          |

| viewing Angles | θ21(   | J)     | $CK \ge 10$          | 50    | 60                                           | -              |        | Note 9-1 |                   |          |

|                | θ22(E  | ))     |                      | 40    | 45                                           | -              |        |          |                   |          |

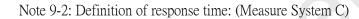

| Response Time  | Tr+Tf  |        | $\Theta = 0^{\circ}$ | -     | 35                                           | 50             | ms     | Note 9-2 |                   |          |

| Contrast Ratio | CR     |        | $\Theta = 0^{\circ}$ | 200:1 | 300:1                                        | -              | -      | Note 9-3 |                   |          |

| Luminance      | L      |        | L                    |       | $\Theta = 0^{\circ}$<br>I <sub>F</sub> =20mA | 240            | 280    | -        | cd/m <sup>2</sup> | Note 9-4 |

| NTSC           | -      |        | -                    | 45    | 50                                           |                | %      | Note 9-4 |                   |          |

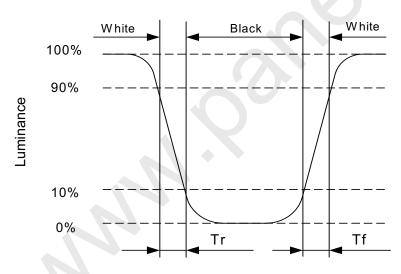

| Uniformity     | -      |        | -                    | 75    | 80                                           | -              | %      | Note 9-5 |                   |          |

|                | Red    | x<br>y |                      | 0.565 | 0.615<br>0.350                               | 0.665<br>0.400 |        |          |                   |          |

|                | Crean  | Х      |                      | 0.290 | 0.34                                         | 0.390          |        |          |                   |          |

| Chusensetisity | Green  | у      | $\Theta = 0^{\circ}$ | 0.509 | 0.559                                        | 0.609          |        | Note 9-6 |                   |          |

| Chromaticity   | Blue   | Х      | $\Theta=0$           | 0.096 | 0.146                                        | 0.196          | -      | Note 9-6 |                   |          |

|                | Diue   | у      |                      | 0.062 | 0.112                                        | 0.162          |        |          |                   |          |

|                | White  | Х      |                      | 0.275 | 0.310                                        | 0.345          |        |          |                   |          |

|                | w mile | у      |                      | 0.290 | 0.330                                        | 0.370          |        |          |                   |          |

The information contained herein is the exclusive property of toppoly Optoelectronics corporation, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of toppoly Optoelectronics corporation.

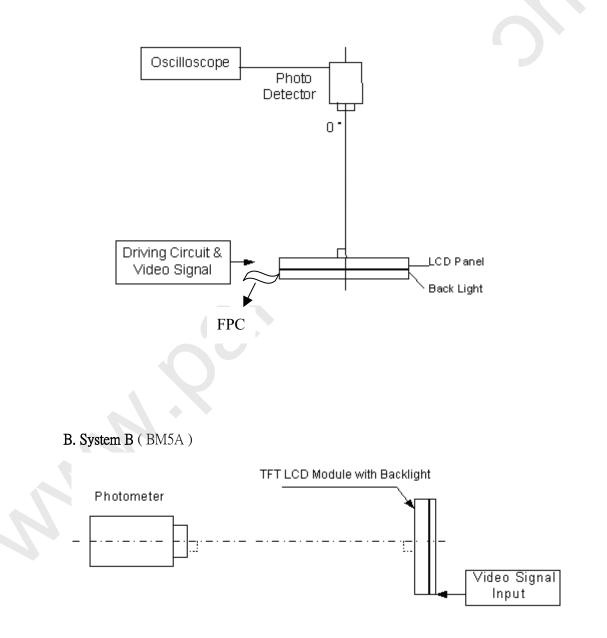

- 9.2 Basic measure condition

- 9.2.1 Driving voltage VDD= 12.0V, VEE=-6.5V

- 9.2.2 Ambient temperature: Ta=25°C

- 9.2.3 Testing point: measure in the display center point and the test angle  $\Theta = 0^{\circ}$

- 9.2.4 Testing Facility

Environmental illumination: ≤ 1 Lux

#### A. System A ( DMS 900 series )

$\langle p \rangle$

Note 9-3: Contrast Ratio in back light on (Measure System A)

Contrast Ration is measured in optimum common electrode voltage.

Luminance with white image Luminance with black image CR =

Note 9-4: Luminance : (Measure System A\_ Spectrum meter)

Test Point: Display Center

(The minimum transmission ratio of touch panel is 80%)

The information contained herein is the exclusive property of toppoly Optoelectronics corporation, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of toppoly Optoelectronics corporation.

Page: 25/37

po

### TD028TTEB5

#### Note 9-5: Uniformity (Measure System B)

The luminance of 9 points as the black dot in the figure shown below are measured and the uniformity is defined as the formula:

Note 9-6: White chromaticity as back light on and NTSC(Measure System A\_Spectrum)

The information contained herein is the exclusive property of toppoly Optoelectronics corporation, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of toppoly Optoelectronics corporation.

屏库:全球液晶屏交易中心

### TD028TTEB5

#### 10. Reliability

tpo

| No | Test Item                                                       | Condition                                |

|----|-----------------------------------------------------------------|------------------------------------------|

| 1  | High Temperature Operation,HTO<br>IEC 68-2-2                    | Ta=60°∁ , 240Hrs                         |

| 2  | High Temperature Storage,HTS<br>IEC 68-2-2                      | Ta=70°C , 240Hrs                         |

| 3  | Low Temperature Operation,LTO<br>IEC 68-2-1                     | Ta=-20℃, 240Hrs                          |

| 4  | Low Temperature Storage,LTS<br>IEC 68-2-1                       | Ta=-30°C , 240Hrs                        |

| 5  | High Temperature & High Humidity<br>Operation,HHO<br>IEC 68-2-3 | Ta=40℃, RH=95%, 240Hrs                   |

| 6  | High Temperature & High Humidity<br>Storage,HHS<br>IEC 68-2-3   | Ta=60℃, RH=90%, 240Hrs                   |

| 7  | Thermal Shock,TS<br>IEC 68-2-14                                 | -30°C (0.5hrs) ←→70°C (0.5hrs), 50Cycles |

| 8  | Low Pressure test - Operation                                   | Operation, 15,000ft(0.52atm) /48hours.   |

The information contained herein is the exclusive property of toppoly Optoelectronics corporation, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of toppoly Optoelectronics corporation.

tpo

### TD028TTEB5

| 9  | Low Pressure test - Non Operation                 | Non-Operation, 40,000ft(0.186atm) /48hours                                                                                                                                                                                                                                                                                                     |

|----|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10 | Storage                                           | 1.60°C (16Hrs)<br>2.25°C, 60%RH, 2Hrs<br>3.90%RH, 25°C→55°C<br>within 3 Hrs, stay 9Hrs<br>at 55°C, 55°C→25°C<br>within 3Hrs, stay 9Hrs<br>at 25°C<br>4.25°C, 60%RH, 2Hrs<br>520°C, 24Hrs<br>6.25°C, 60%RH, 2Hrs<br>7.90%RH, 25°C→55°C<br>within 3 Hrs, stay 9Hrs<br>at 55°C, 55°C→25°C<br>within 3Hrs, stay 9Hrs<br>at 25°C.<br>repeat 2 times |

| 11 | Sine Vibration Test - Operation                   | Sweep rate 0.5 octave/ min. 3 axes, 3 sweep per<br>axis. 5~9 Hz, 6.6mm(P-P), 9~200Hz, 1.0G,<br>200~500Hz,1.5G                                                                                                                                                                                                                                  |

| 12 | Sine Vibration Test - Non Operation<br>IEC 68-2-6 | 5g Zero to peak, Sweep rate 0.5 octave/ min. one<br>sweep, 10~500Hz, all 3 axes(X,Y,Z)                                                                                                                                                                                                                                                         |

| 13 | Random Vibration Test - Operation                 | 3 axes, 30 min per axis, 1.67 grms, 10~200Hz,<br>0.01G^2/Hz, 200~500Hz, 0.003G^2/Hz                                                                                                                                                                                                                                                            |

| 14 | Random Vibration Test - Non Operation             | 0.025G^2/Hz, 10~500Hz, Normal 3.5Grms in each<br>axis                                                                                                                                                                                                                                                                                          |

$\oslash$

| 15 | Shock Test- Non Operation<br>IEC 68-2-27     | Acceleration: 400G; Time: 2.0ms;Directions: ±X, ±Y,<br>±Z; Cycles: one                                                                                                                                                                                                                                                                                                                          |

|----|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16 | Dust Test<br>IEC 68-2-68                     | Condition 1:<br>Temperature Range: 15°C to 35°C<br>Relative Humidity: 25 % to 75 %<br>Air Pressure: 86 kPa to 106 kPa<br>Particle size: 50 micrometer<br>Duration time: 8 hours<br>BS EN 60529: IP5X degree of protection<br>Condition2:<br>The box fills with enough talcum powder to cover up<br>UUT and the<br>box only contain 1 unit. Test shall be continued for a<br>period of 1 minute. |

| 17 | FPC Bending Test<br>IEC 68-2-21              | Connector side : bending angle will be decided per<br>different project .<br>LCD side : bending angle will be decided per<br>different project .<br>Minimum 15 cycles for each side.                                                                                                                                                                                                            |

| 18 | FPC connection Insert/Remove test            | Insert/Remove LCM FPC for 15 cycles.                                                                                                                                                                                                                                                                                                                                                            |

| 19 | Image Retention Test                         | Black/white block interleave pattern<br>in +40°C for 12 hours,<br>residual image should not be found on R,G,B and<br>Black/white block interleave pattern after 120<br>minutes at room temp.                                                                                                                                                                                                    |

| 20 | Touch Panel Writing Friction Resistance Test | After 100,000 cycles (forward – back two way<br>defined as 1 cycle) with<br>a stylus of R0.8 polyacetal (load: 250g) in center of<br>active area and<br>measure it.                                                                                                                                                                                                                             |

The information contained herein is the exclusive property of toppoly Optoelectronics corporation, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of toppoly Optoelectronics corporation.

$\oslash$

|    |                                     | Hit it 1,000,000 times with a silicon rubber of R8  |

|----|-------------------------------------|-----------------------------------------------------|

| 21 | <br>Touch Panel Pin Activation Test | Hs40 and measure it.                                |

| 21 |                                     | The hitting force shall be 250g and hitting speed 3 |

|    |                                     | times per second.                                   |

The information contained herein is the exclusive property of toppoly Optoelectronics corporation, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of toppoly Optoelectronics corporation.

#### 11. Handling Cautions

#### 11.1 ESD (Electrical Static Discharge) strategy

ESD will cause serious damage of the panel, ESD strategy is very important in handling. Following items are the recommended ESD strategy

- 11.1.1 In handling LCD panel, please wear gloves with non-charged material. Using the conduction ring connects wrist to the earth and the conducting shoes to the earth necessary is.

- 11.1.2 The machine and working table for the panel should have ESD protection strategy.

- 11.1.3 In handling the panel, ionized airflow decreases the charge in the environment is necessary.

- 11.1.4 In the process of assemble the module, shield case should connect to the ground.

#### 11.2 Environment

- 11.2.1 Working environment of the panel should be in the clean room.

- 11.2.2 Because touch panel has protective film on the surface, please remove the protection film slowly with ionized air to prevent the electrostatic discharge.

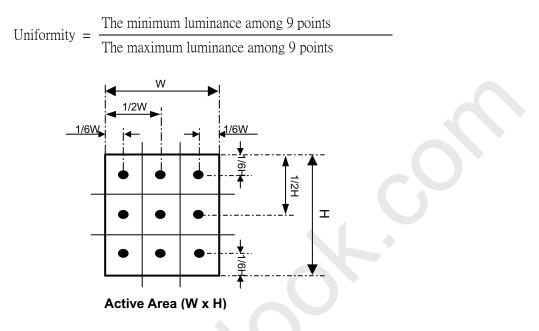

#### 11.3 Touch panel

- 11.3.1 The front touch panel is vulnerable to heavy weight, so any input must be done by special stylus or by a finger. Do not put any heavy stuff on it.

- 11.3.2 When any dust or stain is observed on a film surface, clean it using a glass lens cleaner for something similar.

#### 11.4 Others

- 11.4.1 Turn off the power supply before connecting and disconnecting signal input cable.