## Что такое метастабильное состояние и как с ним бороться?

Проблема синхронизации нескольких асинхронных систем отнимает много времени при разработке микропроцессорных систем. Если же инженер-схемотехник при создании функциональной схемы не понял, что некоторые блоки его системы работают асинхронно, то проблема синхронизации отодвигается на этап отладки. Так начинается болезнь, при которой на одно и то же событие, например на нажатие клавиши, прибор реагирует по-разному.

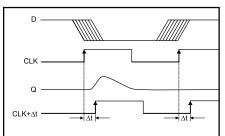

ипичный пример синхронизации — защелкивание сигнала прерывания триггером. Тактовая частота подается на вход триггера СLК, а сигнал прерывания — на вход данных. При совпадении защелкивающего сигнала и момента изменения сигнала данных, триггер входит в метастабильное состояние, на его выходе появляется сигнал неопределенного уровня, и это может привести к ошибке в работе системы.

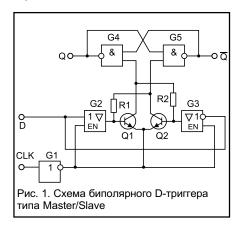

На рис. 1 показана упрощенная схема D-триггера типа ведущий/ведомый (Master/Slave). Если на вход СLК подан лог. 0, то на эмиттерах транзисторов  $\mathbf{Q}_1$  и  $\mathbf{Q}_2$  будет лог. 1 — транзисторы заперты. В зависимости от уровня сигнала на входе D, на базе одного из транзисторов будет лог. 1 при условии, что на вход разрешения En будет подан лог. 0 — инвертированный сигнал CLK. Этот же сигнал

лог. 0, как видно из схемы, будет подан и на эмиттеры транзисторов. Резисторы  $R_1$  и  $R_2$  удерживают транзисторы ведущего триггера в стабильном состоянии. Ведомый триггер устанавливается в новое состояние в зависимости от напряжения на коллекторах транзисторов.

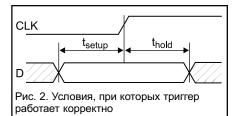

Правильная работа триггера по принципу, описанному выше, гарантируется только в том случае, если выдержано время установки и удержания сигнала D  $t_{\text{SETUP}}$  и  $t_{\text{HOLD}}$  (рис. 2).

В синхронных системах проблемы своевременной установки и удержания сигналов обычно не бывает, так как сигнал в большинстве случаев устанавливается задолго до начала такта и удерживается до спада сигнала СLК. Исключение составляют схемы с высоким быстродействием. В них время установки сигналов во всех компонентах

системы стремятся свести к минимальному. В случае, когда сигнал данных изменяется во время фронта CLK, в асинхронных схемах происходит следующее. При изменении сигнала на входе D. на базе одного транзистора сигнал переходит из состояния лог. О в состояние лог. 1, а на базе другого — наоборот, из состояния лог. 1 в состояние лог. 0. В этот момент напряжения на базах транзисторов практически равны, и ведущий триггер оказывается в неопределенном состоянии — ни в низком, ни в высоком. Как следствие, в таком же состоянии оказывается и ведомый транзистор. Это состояние называется неопределенным или метастабильным.

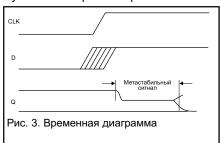

Как видно из рис. 3, выходной сигнал Q тоже не определен. После некоторого времени транзисторы  $\mathbf{Q}_1$  и  $\mathbf{Q}_2$  из-за жесткой обратной связи устанавливаются в определенное состояние, но в какое — сказать трудно, поскольку это зависит от шумов самих транзисторов.

На рис. 4 показаны возможные формы выходного метастабильного сигнала:

А — правильный выходной сигнал;

В — сначала ведомый триггер не распознает метастабильное состояние мастера и начинает переключаться до тех пор, пока мастер не выйдет из метастабильного состояния; на выходе это выглядит как сильно растянутый фронт, и, как показывает практика, при этом задержка получается довольно большой;

С — ведущий триггер в метастабильном состоянии переключает ведомый, и на его выходе появляется высокий уровень; если ведущий триггер возвращается в нормальное состояние, на выходе ведомого триггера снова появляется низкий уровень.

Инвертированный сигнал D даст те же самые диаграммы. Феномен, рассмотренный здесь, описан в контексте биполярных микросхем, но также встречается в микросхемах КМОП и БиКМОП.

Анализ метастабильного состояния триггеров — не простое занятие. Причина этого в том, что время фронта сигнала СLК очень мало и часто не превышает 1 нс. Результатом такого анализа должно являться сообщение о том, насколько часто будет сбоить схема.

Среднее время между сбоями — MTBF (Mean Time Between Failures) — зависит от частоты синхронного и асинхронного сигналов и длительности критического окна (время установки и удержания сигнала приводится в документации в зависимости от последнего параметра): MTBF =  $1/f_{\rm IN} \cdot f_{\rm CLK} \cdot f_{\rm D}$ .

Например, при частотах  $f_{\rm IN}=1$  кГц,  $f_{\rm CLK}=1$  МГц и критическом времени  $t_{\rm D}=30$  нс, среднее время между сбоями составляет 33 с — вполне ощутимая величина, достаточная для того, чтобы вычислить и исправить ошибку во время отладки, а не после серийного выпуска прибора.

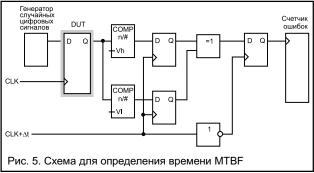

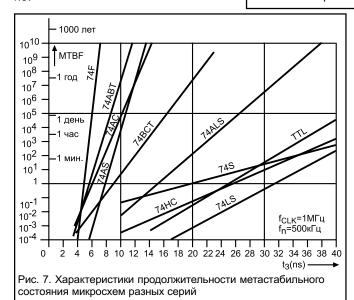

Время МТВF зависит от серии микросхем. Каждая из них имеет свое время  $t_{\rm D}$ . Для того чтобы оценить величину МТВF и продолжительность метастабильного состояния, в котором находится триггер, можно построить испытательный стенд (рис. 5).

На вход D подается случайный цифровой сигнал, вход CLK тактируется. Два компаратора сравнивают выходной сигнал с эталонным сигналом низкого или высокого уровня. Если обнаружен метастабильный сигнал, то

вентиль "исключающее ИЛИ" срабатывает и увеличивает значение счетчика ошибок. Для того чтобы вычислить частоту появления ошибок с заданной продолжительностью метастабильного состояния, в цепь вводят триггеры, на которые тактовый сигнал поступает с некоторой задержкой, так что ошибки с метастабильным состоянием, которое меньше времени задержки, не регистрируются (рис. 6).

Рис. 6. Регистрация ошибок при метастабильном состоянии заданной продолжительности

На рис. 7 показано, как количество встречающихся ошибок в схемах зависит от серии. Следует отметить также прогнозируемость времени метастабильного состояния. Серии F (Fast) и АВТ дают ошибки одной и той же продолжительности — не более 6 и 11 нс соответственно, а продолжительность метастабильного состояния серий 74S и 74HC в течение даже одних суток определить очень трудно.

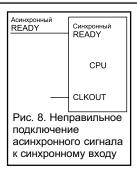

внутренней защиты от ситуации, когда изменение сигнала тактовой частоты совпадает с изменением сигнала запроса прерывания. Это явно или не-

явно оговаривается в документации на процессор, где указывается время установки и удержания сигнала.

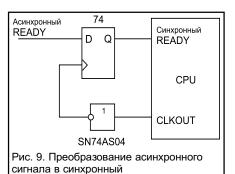

При подключении асинхронного сигнала ко входу, который тактируется внутри процессора тактовой частотой, возникает ошибка. Ее можно избежать, если подключить ко входу процессора дополнительный триггер (рис. 9).

Реально при таком подключении работает схема, показанная на рис. 10. В ней два триггера: один находится внут-

Предложенное решение на практике исключает появление неопределенных сигналов в системе. Теоретически такой сигнал на выходе первого триггера может продолжаться более одного такта, и тогда в метастабильном состоянии окажется второй триггер. Вероятность ошибки можно определить из графика продолжительности метастабильных состояний микросхем разных серий, и при тактовой частоте в 50 МГц эта ошибка может встретиться один раз в миллион лет при использовании "благонадежных" в этом отношении микросхем (см. рис. 7).

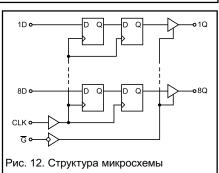

Проблема синхронизации систем встречается довольно часто. И это вызвало потребность в создании микросхем, предназначенных для ее решения. На рис. 12 показана логическая структура микросхемы синхронизации, состоящей из двух триггеров, тактируемых одним сигналом — SN74AS374B.

Проблема метастабильности считается проблемой микросхем ранних серий ТТЛ из-за большого времени установки и удержания защелкиваемых

## Механизм появления метастабильных состояний

На рис. 8 показана типичная схема, в которой может возникнуть метастабильное состояние на выходе, которое повлечет за собой системную ошибку. Вход готовности системы Ready тактируется внутренней тактовой частотой. На этот тактируемый вход следует подать сигнал, который защелкнется по сигналу CLKOut. Большинство процессоров не имеет

ри процессора, другой — вне его. Оба тактируются сигналом CLKOut.

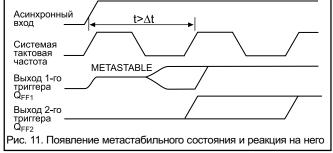

Асинхронный сигнал при этом запаздывает на один такт. Когда частота асинхронного сигнала совпадает с тактовой частотой

процессора, выход первого триггера находится в метастабильном состоянии. До начала нового такта первый триггер выходит из метастабильного состояния в какое-либо определенное состояние, и в случае, когда его новое состояние соответствует состоянию сигнала на входе, асинхронный сигнал запаздывает на один такт синхронизации. В худшем случае асинхронный сигнал запаздывает на два такта (рис. 11).

сигналов. Нужно быть осторожным при использовании серий S, LS и HC. Серии AS, F, AC и ABT считаются более надежными в этом смысле.

Вадим Стрижов, strijov@ccas.ru