| Микроконтроллеры, АЦП, память и т.д Темы касающиеся микроконтроллеров разных производителей, памяти, АЦП/ЦАП, периферийных модулей... |

30.12.2006, 01:07

30.12.2006, 01:07

|

|

|

Временная регистрация

Регистрация: 16.06.2006

Адрес: Даугавпилс

Сообщений: 52

Сказал спасибо: 1

Сказали Спасибо 0 раз(а) в 0 сообщении(ях)

|

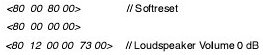

А это из даташита.

-- Прилагается рисунок: --

|

|

|

|

30.12.2006, 02:05

30.12.2006, 02:05

|

|

|

Временная регистрация

Регистрация: 16.06.2006

Адрес: Даугавпилс

Сообщений: 52

Сказал спасибо: 1

Сказали Спасибо 0 раз(а) в 0 сообщении(ях)

|

Вообщем то конкретный вопрос такой: полноценный ли в 8 меге аппаратный I2C? Поддерживает ли он задержку клока при передаче команд устройству с более медленной шиной?

|

|

|

|

30.12.2006, 03:41

30.12.2006, 03:41

|

|

|

Прописка

Регистрация: 03.08.2006

Сообщений: 267

Сказал спасибо: 0

Сказали Спасибо 4 раз(а) в 2 сообщении(ях)

|

Не вполне владею инструментами протеуса, поэтому прошу извинить за следующие наводящие вопросы и уточнения, надеюсь, они помогут решить Вашу задачу.

1. Проблемы с отладкой связи с устройством наблюдаются в протеусе или в реальном железе? В протеусе случается не 100% соответствие имитации работы реальных микросхем.

2. В прилагаемом рисунке S-старт условие, P-стоп условие, Sr-опечатка?, N - ACK ведомого и лог. 0 ???

Согласно протоколу I2C, при операции записи в ведомое устройство, ACK, логическим нулём, формирует ведомый. При операции чтения из ведомого (не путать с записью команды чтения), ACK, логическим нулём, формирует ведущий. Ведущий формирует NACK логической единицей после приёма последнего байта от ведомого, перед выдачей стоп условия. Ведомый, в моменты своей неготовности к обмену, может удерживать сигнал шины CLK в 0, ведущий, при этом, должен ожидaть перехода сигнала CLK из 0 в 1. MSP 34x0G, судя по описанию, может удерживать этот сигнал в нуле до 1 мСек при каждом обращении к физическому адресу устройства (записи - чётн. адр. или чтения - адр.+1).

3. Установлены ли в схеме PullUp резисторы в цепях CLK и DTA?

4. Как инициализированы линии TWI?

На шине I2C активны только нулевые уровни сигнала, единица - только через PullUp. Поэтому предельная скорость шины взаимосвязана с длиной соединительных проводников, ёмкостью и индуктивностью монтажа и номиналом этих резисторов.

5. Шина I2C тактируется с меньшей частотой чем 1МГц (это максимально допустимая величина для шины I2C в MSP 34x0G)?

С уважением, Mike18.

|

|

|

|

30.12.2006, 03:52

30.12.2006, 03:52

|

|

|

Прописка

Регистрация: 03.08.2006

Сообщений: 267

Сказал спасибо: 0

Сказали Спасибо 4 раз(а) в 2 сообщении(ях)

|

|

Сообщение от LDZ

|

|

Вообщем то конкретный вопрос такой: полноценный ли в 8 меге аппаратный I2C? Поддерживает ли он задержку клока при передаче команд устройству с более медленной шиной?

|

Извините, отстал с ответом на два сообщения пока с предыдущим разбирался  . Про Мегу, к сожалению, ничего сказать не могу. Обстоятельства сложились так, что применять не доводилось. По-идее, шина I2C, изначально асинхронная, и ведущий должен для продолжения тактирования дождаться перехода CLK из 0 в 1, думаю, что даже такты пустые может при этом пропускать. Скорость на шине I2C, реально, всегда ниже установленной (и настроенной) в контроллере из-за влияния переходных процессов (задержка перехода CLK из 0 в 1 при заряде ёмкости этой цепи через PullUp резисторы; интервал следования CLK из-за этого, даже от такта к такту, может отличаться). По крайней мере у контроллеров Microchip это происходит именно так.

С уважением Mike18.

|

|

|

|

30.12.2006, 14:52

30.12.2006, 14:52

|

|

|

Временная регистрация

Регистрация: 16.06.2006

Адрес: Даугавпилс

Сообщений: 52

Сказал спасибо: 1

Сказали Спасибо 0 раз(а) в 0 сообщении(ях)

|

Что есть: 1. протеус, MSP в нем нет, линии в воздухе, поэтому дебуггер и показывает S-Sr-NACK. 2. реальное устройство с данной микрухой. При снятии лога четко видно, что 0 на клоке шире 1 - т.е. MSP реально тормозит клок до ,примерно 45Кгц. 3. моя мега подключается к MSP посредством шлейфика длинной около 40 см. Дороги к родному процу отпаяны. На шине внешние резюки 3к3 на +5в. Торможения клока не заметил. Скорость пробывал разную. АСК есть - смотрел цифровым осцилком, вычитывал в меге регистр TWSR. В этом месте все пучком. А вот на команды MSP реагировать не хочет.

|

|

|

|

30.12.2006, 20:12

30.12.2006, 20:12

|

|

|

Прописка

Регистрация: 03.08.2006

Сообщений: 267

Сказал спасибо: 0

Сказали Спасибо 4 раз(а) в 2 сообщении(ях)

|

|

Сообщение от LDZ

|

|

... А вот на команды MSP реагировать не хочет.

|

Вы не пробовали выполнить примеры минимальных кодов инициализации из раздела 3.5 даташита MSP?

|

|

|

|

30.12.2006, 23:08

30.12.2006, 23:08

|

|

|

Временная регистрация

Регистрация: 16.06.2006

Адрес: Даугавпилс

Сообщений: 52

Сказал спасибо: 1

Сказали Спасибо 0 раз(а) в 0 сообщении(ях)

|

Посылал ему и это. Хотя в реальном устройстве при регулировке громкости среди всех посылок на 80й адрес идет одна - именно на громкость. Без всяких софтресетов и прочего.

|

|

|

|

31.12.2006, 03:00

31.12.2006, 03:00

|

|

|

Прописка

Регистрация: 03.08.2006

Сообщений: 267

Сказал спасибо: 0

Сказали Спасибо 4 раз(а) в 2 сообщении(ях)

|

Допускает ли установленное состояние выводов RESETQ, STANDBYQ, TESTEN и ADR_SEL управление MSP? Имеется ли необходимая генерация на выводах XTAL_OUT и XTAL_IN? Соблюдаются ли необходимые условия работы шины (см. 4.6.3.4. I2C-Bus Characteristics и Fig. 4–25: I2C bus timing diagram в даташит MSP)?

У ATMEL имееттся ещё один пример реализации ведущего I2C (AVR315). Вот ссылка на перевод этого AN: http://www.gaw.ru/html.cgi/txt/app/m...avr/AVR315.htm

С уважением, Mike18.

|

|

|

|

31.12.2006, 13:00

31.12.2006, 13:00

|

|

|

Временная регистрация

Регистрация: 16.06.2006

Адрес: Даугавпилс

Сообщений: 52

Сказал спасибо: 1

Сказали Спасибо 0 раз(а) в 0 сообщении(ях)

|

Выводы в рабочем состоянии. ADR - на 80,81(земля).

Кварц генерит. По поводу тайминга. Я так понимаю, что они заложены уже в железо и изменить их нельзя. Сомнения только в Data Hold Time - min 55ns у МSР и

0-3.45us у меги. Хотя главное условие - неизменное состояние шины данных остается. Принцип работы TWI также описан в даташите. Он и используется в апноутах.

Разве имеет значение каким образом данные попадут в регистр TWDR?

|

|

|

|

Ваши права в разделе

Ваши права в разделе

|

Вы не можете создавать новые темы

Вы не можете отвечать в темах

Вы не можете прикреплять вложения

Вы не можете редактировать свои сообщения

HTML код Выкл.

|

|

|

| Тема |

Автор |

Раздел |

Ответов |

Последнее сообщение |

|

ATMega 8 + TWI

|

_OXY_GEN_ |

Микроконтроллеры, АЦП, память и т.д |

4 |

03.06.2009 17:33 |

|

TWI в AVR

|

igor727 |

Микроконтроллеры, АЦП, память и т.д |

0 |

21.05.2008 19:15 |

|

Пример использования TWI для AVR

|

EXIS |

Микроконтроллеры, АЦП, память и т.д |

2 |

27.02.2008 21:16 |

|

TWI as master и USI as slave

|

duritskiy |

Микроконтроллеры, АЦП, память и т.д |

20 |

06.09.2007 19:18 |

|

ATmega168: TWI + WatchDog < > любовь

|

Diusha |

Микроконтроллеры, АЦП, память и т.д |

6 |

27.10.2006 07:46 |

Часовой пояс GMT +4, время: 23:03.

|

|