LS1021A — новый коммуникационный процессор семейства QorIQ LS1 на базе ядра ARM мощностью потребления менее 3 Вт |

|

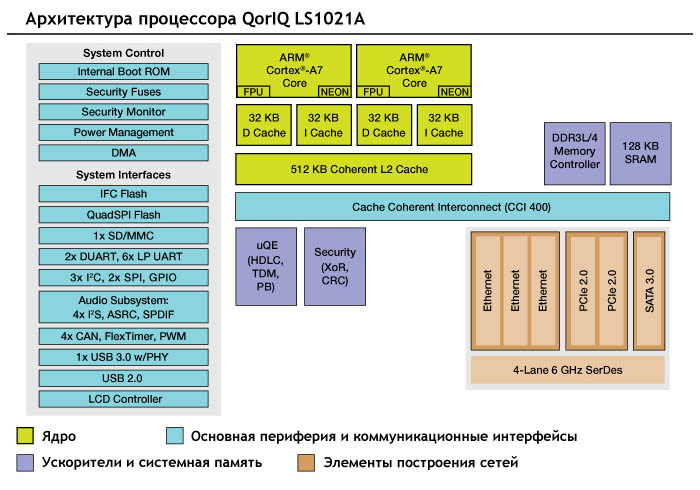

Интегрируя два ядра ARM® Cortex®-A7 с кодом коррекции ошибок (ECC) и рабочей частотой до 1 ГГц, процессор QorIQ LS1021A обеспечивает расчетную производительность более 6000 CoreMark®, функции аппаратной виртуализации, защищенной начальной загрузки и доверенной архитектуры, а также широчайший набор высокоскоростных коммуникационных интерфейсов и оптимизированной периферии, когда-либо реализованных в процессорах с мощностью потребления менее 3 Вт.

|

Беспрецедентный уровень интеграции

Семейство процессоров QorIQ LS1 специально разработано для применения в новом поколении устройств с ограниченным энергопотреблением, объединив в себе энергоэффективность ядра ARM и более чем 12-летний опыт Freescale в сетевых коммуникационных технологиях и интеграции IP-блоков функций, с целью предложить пользователям высочайший уровень интеграции в единой системе мощностью потребления менее 3 Вт. Благодаря встроенному коду коррекции ошибок для кэш-памяти первого (L1) и второго (L2) уровней, поддержке архитектуры QUICC, передовому интерфейсу USB 3.0 и широкому набору высокоскоростных коммуникационных интерфейсов и периферийных модулей, процессоры QorIQ LS1 являются оптимальным выбором для многоядерных платформ, которым необходимо обеспечить более защищенный, интеллектуальный и эффективный режим работы без снижения производительности.

Процессорное ядро

Процессор QorIQ LS1021A интегрирует два ядра ARM Cortex-A7 с рабочей частотой 1 ГГц и кодом коррекции ошибок (ECC) для кэш-памяти первого и второго уровней. Оба ядра поддерживают по 32 Кбайт кэш-памяти данных и 32 Кбайт кэш-памяти инструкций первого уровня, совместно используют 512 Кбайт кэш-памяти второго уровня, оснащены модулями NEON SimD и блоками цифровой обработки сигналов (DSP) с плавающей точкой (FPU) двойной точности. Контроллер памяти DDR3L/4 поддерживает до четырех устройств с шириной шины 8, 16 или 32 бита на частоте до 1600 МГц.

Системные и коммуникационные интерфейсы

4-канальный, мультипротокольный сериализатор/десериализатор (SerDes) с рабочей частотой до 6 ГГц обеспечивает поддержку высокоскоростных интерфейсов, включая три порта Gigabit Ethernet с поддержкой IEEE® 1588, два порта PCI Expree® 2.0 управляемых DMA-контроллером и один порт SATA 3.0. Процессор LS1021A также оснащен двумя контроллерами USB интерфейса — один из которых поддерживает протокол SuperSpeed USB 3.0 и интегрированный физический уровнем, а другой — USB 2.0. Помимо этого реализована поддержка интерфейсов QuadSPI, IFC и карт памяти SD/MMC. Для сетевых аудио приложений LS1021A поддерживает интерфейсы ASRC и SPDIF. Для промышленных приложений процессор оснащен 4-канальным контроллером CAN интерфейса и поддерживает до 10 каналов UART для работы с различными промышленными протоколами. К дополнительным последовательным интерфейсам относятся 3-канальный I2C и 2-канальный SPI.

Масштабируемость

Основным преимуществом процессоров QorIQ, построенных на архитектуре Layerscape, является полная совместимость их функциональных особенностей, включая функции визуализации и когерентность кэш-памяти, а также единая система команд процессоров QorIQ LS1. Это, наряду с полной совместимостью по назначению выводов и программному коду с другими процессорами семейства LS1 — LS1020A и LS1022A — позволяет разработчикам с легкостью портировать свои приложения на новые поколения процессоров семейства QorIQ.

Отличительные особенности:

- Два высокопроизводительных ядра ARM Cortex-A7 с DSP-блоками вычислений с плавающей точкой двойной точности и модулем набора команд NEON SimD

- Кэш-память второго уровня общего пользования объёмом 512 КБ

- Контроллер памяти DDR с поддержкой модулей DDR3L и DDR4 с частотой до 1600 МГц

- Три виртуальных Ethernet-контроллера с утроенной скоростью передачи данных

- Два контроллера шины PCIe 2.0

- Интерфейс USB3.0 с интегрированным физическим уровнем PHY

- Интерфейсы SATA3, CAN, протокол канального уровня HDLC/технология мультиплексирования с разделением во времени (TDM), SPI, I2C, I2S и 10 интерфейсов UART

- Защищенный блок начальной загрузки

- Доверенная архитектура и поддержка расширения безопасности ARM TrustZone, включая защиту от несанкционированного доступа и копирования

| Источник: www.gaw.ru | Дата публикации: 10/08/2014 |

|  |

|

Реклама на сайте |

|

Последние новости  |

[06/02/2019] Конференция в МГТУ им. Баумана «Технологии разработки и отладки сложных технических систем» 2019

[09/05/2018] Грандиозная майская распродажа на Gearbest!

[16/05/2017] С 15 по 17 мая в магазине Gearbest проходит грандиозный флэшсейл

[10/05/2017] Так что же такое Спиннер?

[05/12/2016] Новый Год и Рождество с GearBest!

[29/09/2016] Всемирный День Интернета на GearBest

Читать все новости >> |